Hi @vix,

I tested myself here and this can be accomplished with the image.json inside the image file. Since we’re dealing with U-Boot, TorizonCore Builder is not useful, since we can’t change U-Boot setting with it.

In this case, I simply added a few lines to my image.json and the u-boot-initial-end-sd files.

Here are the steps:

- First, I downloaded an image from our feed,

torizon-core-docker-verdin-imx8mm-Tezi_6.1.0+build.1 in my case, but you can choose a different one.

- Next, I moved my Cortex-M binary inside this folder:

.rwxr-xr-x 6,260 hiago hiago 23 Mar 16:34 hello_world.bin

.rw-r--r-- 1,566 hiago hiago 23 Mar 16:41 image.json

.rw-r--r-- 1,314,376 hiago hiago 16 Jan 11:29 imx-boot

.rw-r--r-- 79,368 hiago hiago 16 Jan 12:00 LA_OPT_NXP_SW.html

.rw-r--r-- 212,480 hiago hiago 16 Jan 11:33 marketing.tar

.rw-r--r-- 183 hiago hiago 16 Jan 11:33 prepare.sh

.rw-r--r-- 2,488 hiago hiago 16 Jan 11:33 toradexlinux.png

.rw-r--r-- 217,362,695 hiago hiago 16 Jan 11:59 torizon-core-docker-verdin-imx8mm.ota.tar.zst

.rw-r--r-- 4,232 hiago hiago 23 Mar 16:35 u-boot-custom-env-sd

.rw-r--r-- 4,127 hiago hiago 16 Jan 10:04 u-boot-initial-env-sd

.rw-r--r-- 18 hiago hiago 16 Jan 11:33 wrapup.sh

- Now, you need to edit the image.json to copy the binary when Toradex Easy Installer is going to install your image.

--- image.json.old 2023-03-24 13:43:59.939387885 -0300

+++ image.json 2023-03-23 16:41:59.023515994 -0300

@@ -30,7 +30,8 @@

"filesystem_type": "ext4",

"mkfs_options": "-E nodiscard",

"filename": "torizon-core-docker-verdin-imx8mm.ota.tar.zst",

- "uncompressed_size": 599.375

+ "uncompressed_size": 599.375,

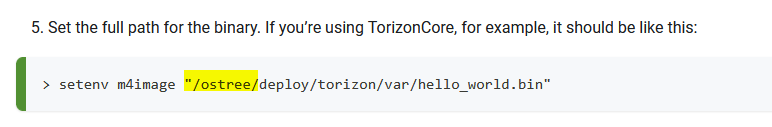

+ "filelist": ["hello_world.bin:/ostree/deploy/torizon/var/"]

}

}

]

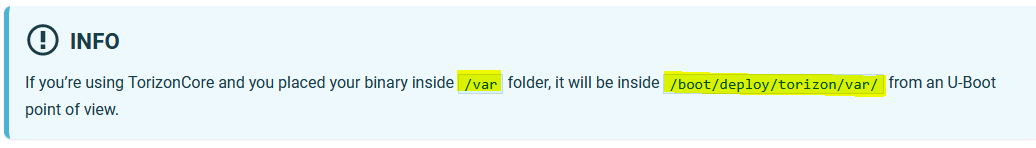

So in this case I’m telling Toradex Easy Installer to move m binary to /var/ when it’s going to install TorizonCore.

- Finally, I added the variables to

u-boot-initial-env-sd to automatically start the auxiliary core.

--- u-boot-initial-env-sd 2023-01-16 10:04:52.846678207 -0300

+++ u-boot-custom-env-sd 2023-03-23 16:35:53.519128019 -0300

@@ -1,4 +1,4 @@

-bootcmd=run bootcmd_mmc0

+bootcmd=run m4boot; run bootcmd_mmc0

bootdelay=1

baudrate=115200

ethprime=FEC

@@ -53,5 +53,6 @@

initrd_high=0xffffffffffffffff

setup=setenv setupargs console=tty1 console=${console},${baudrate} consoleblank=0 earlycon

update_uboot=askenv confirm Did you load flash.bin (y/N)?; if test "$confirm" = "y"; then setexpr blkcnt ${filesize} + 0x1ff && setexpr blkcnt ${blkcnt} / 0x200; mmc dev 0 1; mmc write ${loadaddr} 0x2 ${blkcnt}; fi

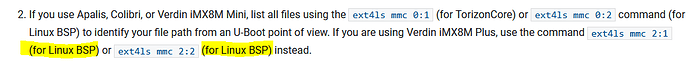

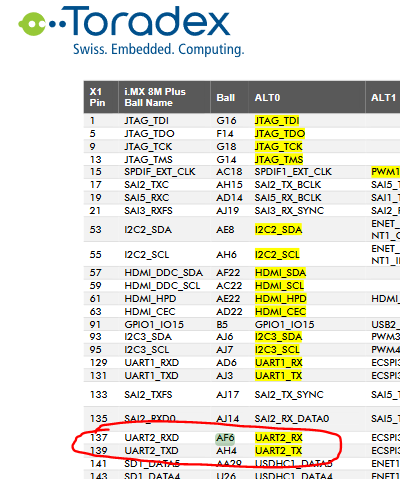

+m4boot=load mmc 0:1 ${loadaddr} 0x7e0000; cp.b ${loadaddr} 0x7e0000 10000; bootaux 0x7e0000;

In this case, I assume you’re using TCM memory, that’s why I used 0x7e0000.

After flashing the image, your binary will be in place and will also be started automatically.

I also did a test with the platform and did an OS update and the Cortex-M kept working. I’m not sure what’s going to happen if you do a bootloader remote update, because we need to make sure u-boot saves this custom m4boot variable.

Hope this helps.

Best Regards,

Hiago.