CoM Model: Toradex Apalis iMX8 QuadMax 8GB Wi-Fi / BT IT V1.1A

Board : Ixora Carrier Board

dear support team,

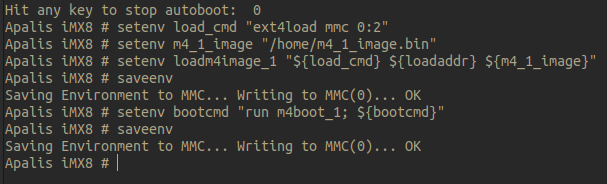

I have an issue when running Cortex-M4 and Cortex-A simultaneously. the initial condition I tried was using BSP 7.1.0 and running FreeRTOS_hello example. I followed the following guide freertos-on-the-cortex-m4-of-an-apalis-imx8 to run FreeRTOS and hello-world-cortexM to customize devicetree overlays for imx8. Then I setup u-boot to run cortex-m4_1 automatically (because on the ixora board only uart on core 1 is supported by default).

but there is no error at all during booting but there is inconsistency when booting. sometimes when rebooted cortex-A can boot immediately and the most common case is infinite booting. In both cases, the Cortex-M stops operating when cortex-A boots and the kernel repeats booting at the position like the following message (most cases).

loop_booting_when_load_M4 (71.2 KB)

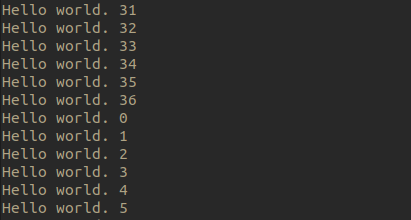

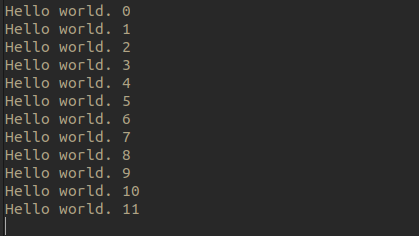

and the following image is the condition of the Cortex-M4_1 serial repeating the counting I did with a 200ms delay

is there any issue related to load cortex-M4 in BSP 7? or for imx8qm it can only run in BSP 5 like the source I read below?

apalis-imx8qm-rpmsg-issue-on-bsp-5-0

but after I tried BSP 5.7.6, I also still have problems with adding overlays. whereas in BSP 7 it works fine.

Applying Overlay: apalis-imx8_M4-Core-0_UART_overlay.dtbo

1543 bytes read in 21 ms (71.3 KiB/s)

Applying Overlay: apalis-imx8_M4-Core-1_UART_overlay.dtbo

593 bytes read in 23 ms (24.4 KiB/s)

failed on fdt_overlay_apply(): FDT_ERR_NOTFOUND

10432345 bytes read in 327 ms (30.4 MiB/s)

Uncompressed size: 24695296 = 0x178D200

Bootargs: pci=nomsi root=PARTUUID=59ccb610-02 ro rootwait

ERROR: Did not find a cmdline Flattened Device Tree

FDT and ATAGS support not compiled in - hanging

### ERROR ### Please RESET the board ###

and here I attach the device tree overlays that I use

- Core 0

/dts-v1/;

/plugin/;

/* Disable UART1 Control Pins to use M4 Core 0 and 1 UART */

/ {

compatible = "toradex,apalis-imx8";

};

&iomuxc {

pinctrl-0 = <&pinctrl_cam1_gpios>, <&pinctrl_dap1_gpios>,

<&pinctrl_esai0_gpios>, <&pinctrl_fec2_gpios>,

<&pinctrl_gpio3>, <&pinctrl_gpio4>, <&pinctrl_gpio_keys>,

<&pinctrl_gpio_usbh_oc_n>,

<&pinctrl_lvds0_i2c0_gpio>, <&pinctrl_lvds1_i2c0_gpios>,

<&pinctrl_mipi_dsi_0_1_en>, <&pinctrl_mipi_dsi1_gpios>,

<&pinctrl_mlb_gpios>, <&pinctrl_qspi1a_gpios>,

<&pinctrl_sata1_act>, <&pinctrl_sim0_gpios>,

<&pinctrl_usdhc1_gpios>;

};

- Core 1

/dts-v1/;

/plugin/;

/* Disable PWM0 and PMW1 to use M4 Core 1 UART */

/ {

compatible = "toradex,apalis-imx8-v1.1-eval",

"toradex,apalis-imx8-eval",

"toradex,apalis-imx8",

"fsl,imx8qm";

};

&lsio_pwm0 {

status = "disabled";

};

&lsio_pwm1 {

status = "disabled";

};

&lpuart2 {

status = "disabled";

};

apalis-imx8_M4-Core-1_UART_overlay.dts (357 Bytes)

apalis-imx8_M4-Core-0_UART_overlay.dts (664 Bytes)

Best Regards,

Azka