Hello @alex.tx

Thank you for your answer.

I cant find some example for that ,right i dont have their physical register addrese !!

Can you guide me, if i want to write CSI block Register Status in the driver ,where can i do that??

in the /kernel-source/drivers/staging/media/imx/imx8-mipi-csi2.c/imx8-mipi-csi2.c( mxc_mipi_csi2_reg_dump(csi2dev) )

static void mxc_mipi_csi2_reg_dump(struct mxc_mipi_csi2_dev *csi2dev)

{

struct device *dev = &csi2dev->pdev->dev;

struct {

u32 offset;

const char name[32];

} registers[] = {

{ 0x100, "MIPI CSI2 HC num of lanes" },

{ 0x104, "MIPI CSI2 HC dis lanes" },

{ 0x108, "MIPI CSI2 HC BIT ERR" },

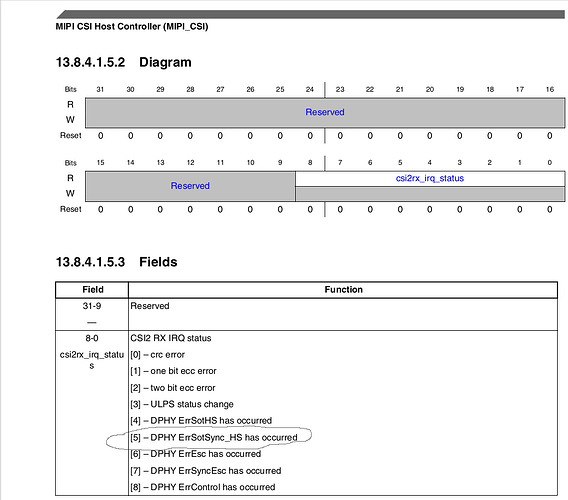

{ 0x10C, "MIPI CSI2 HC IRQ STATUS" },

{ 0x110, "MIPI CSI2 HC IRQ MASK" },

{ 0x114, "MIPI CSI2 HC ULPS STATUS" },

{ 0x118, "MIPI CSI2 HC DPHY ErrSotHS" },

{ 0x11c, "MIPI CSI2 HC DPHY ErrSotSync" },

{ 0x120, "MIPI CSI2 HC DPHY ErrEsc" },

{ 0x124, "MIPI CSI2 HC DPHY ErrSyncEsc" },

{ 0x128, "MIPI CSI2 HC DPHY ErrControl" },

{ 0x12C, "MIPI CSI2 HC DISABLE_PAYLOAD" },

{ 0x130, "MIPI CSI2 HC DISABLE_PAYLOAD" },

{ 0x180, "MIPI CSI2 HC IGNORE_VC" },

{ 0x184, "MIPI CSI2 HC VID_VC" },

{ 0x188, "MIPI CSI2 HC FIFO_SEND_LEVEL" },

{ 0x18C, "MIPI CSI2 HC VID_VSYNC" },

{ 0x190, "MIPI CSI2 HC VID_SYNC_FP" },

{ 0x194, "MIPI CSI2 HC VID_HSYNC" },

{ 0x198, "MIPI CSI2 HC VID_HSYNC_BP" },

{ 0x000, "MIPI CSI2 CSR PLM_CTRL" },

{ 0x004, "MIPI CSI2 CSR PHY_CTRL" },

{ 0x008, "MIPI CSI2 CSR PHY_Status" },

{ 0x010, "MIPI CSI2 CSR PHY_Test_Status" },

{ 0x014, "MIPI CSI2 CSR PHY_Test_Status" },

{ 0x018, "MIPI CSI2 CSR PHY_Test_Status" },

{ 0x01C, "MIPI CSI2 CSR PHY_Test_Status" },

{ 0x020, "MIPI CSI2 CSR PHY_Test_Status" },

{ 0x030, "MIPI CSI2 CSR VC Interlaced" },

{ 0x038, "MIPI CSI2 CSR Data Type Dis" },

{ 0x040, "MIPI CSI2 CSR 420 1st type" },

{ 0x044, "MIPI CSI2 CSR Ctr_Ck_Rst_Ctr" },

{ 0x048, "MIPI CSI2 CSR Stream Fencing" },

{ 0x04C, "MIPI CSI2 CSR Stream Fencing" },

};

u32 i;

pr_info("mxc_mipi_csi2_reg_dump\n");

dev_dbg(dev, "MIPI CSI2 CSR and HC register dump, mipi csi%d\n", csi2dev->id);

for (i = 0; i < ARRAY_SIZE(registers); i++) {

u32 reg = readl(csi2dev->base_regs + registers[i].offset);

dev_dbg(dev, "%20s[0x%.3x]: 0x%.3x\n",

registers[i].name, registers[i].offset, reg);

}

}

I found a function to debug register status , but it just shows the status when the start( mxc_mipi_csi2_reg_dump(csi2dev) ) !!

static int mipi_csi2_s_stream(struct v4l2_subdev *sd, int enable)

{

struct mxc_mipi_csi2_dev *csi2dev = sd_to_mxc_mipi_csi2_dev(sd);

struct device *dev = &csi2dev->pdev->dev;

int ret = 0;

dev_dbg(&csi2dev->pdev->dev, "%s: %d, csi2dev: 0x%x\n",

__func__, enable, csi2dev->flags);

if (enable) {

pm_runtime_get_sync(dev);

if (!csi2dev->running++) {

pr_info("mipi_csi2_s_stream__pm_runtime_get_sync\n");

mxc_csi2_get_sensor_fmt(csi2dev);

mxc_mipi_csi2_hc_config(csi2dev);

mxc_mipi_csi2_reset(csi2dev);

mxc_mipi_csi2_csr_config(csi2dev);

mxc_mipi_csi2_enable(csi2dev);

mxc_mipi_csi2_reg_dump(csi2dev);

}

} else {

if (!--csi2dev->running)

mxc_mipi_csi2_disable(csi2dev);

pm_runtime_put(dev);

}

return ret;

}

If i want to debug CSI register status at kernel mode as dynamic no just when the start ,where can i do that??

Thank you in advance.