Hi,

I’m using the Verdin AM62 module on our custom development board, running in the Yocto environment. I’ve configured one GPIO pin (for example, SODIMM_52 → gpiochip2 line 0) as an input in the device tree.

However, when I check the GPIO state from user space using:

gpioget --chip /dev/gpiochip2 0

it always shows:

"0" = inactive

even when I apply a high signal to that pin.

Could you please let me know if there’s something specific about reading GPIO states from user space on this module, or if any additional configuration (like pull-up/down settings) is needed?

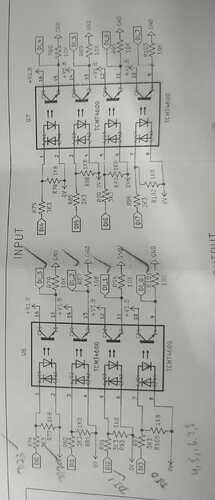

Below is my device tree file for the reference

dts (37.1 KB)

The SODIMM pins configured as inputs are:

52, 54, 56, 58, 60, 62, 66, and 76.

only 66 and 76 is working rest of the things not working

Could you please help me check if there’s anything missing or incorrect in the GPIO configuration?

Also, is there any additional step required to properly read GPIO input states from user space on Verdin AM62?

For reference, my GPIO output configuration using gpio-hog works perfectly fine. For example

myled_sodimm_70 {

label = "my_led_sodimm_70";

gpios = <&main_gpio1 43 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "heartbeat";

default-state = "off";

};

myled_sodimm_72 {

label = "my_led_sodimm_72";

gpios = <&main_gpio1 42 GPIO_ACTIVE_HIGH>;

linux,default-trigger = "heartbeat";

default-state = "off";

};

for quick check kindly refer main part in the device tree as below

/* Verdin QSPI_1_CLK as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_clk_gpio: main-gpio0-0-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x0000, PIN_INPUT, 7) /* (H24) OSPI0_CLK.GPIO0_0 */ /* SODIMM 52 */

>;

};

/* Verdin QSPI_1_CS# as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_cs_gpio: main-gpio0-11-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x002c, PIN_INPUT, 7) /* (F23) OSPI0_CSn0.GPIO0_11 */ /* SODIMM 54 */

>;

};

/* Verdin QSPI_1_IO0 as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_io0_gpio: main-gpio0-3-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x000c, PIN_INPUT, 7) /* (E25) OSPI0_D0.GPIO0_3 */ /* SODIMM 56 */

>;

};

/* Verdin QSPI_1_IO1 as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_io1_gpio: main-gpio0-4-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x0010, PIN_INPUT, 7) /* (G24) OSPI0_D1.GPIO0_4 */ /* SODIMM 58 */

>;

};

/* Verdin QSPI_1_IO2 as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_io2_gpio: main-gpio0-5-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x0014, PIN_INPUT, 7) /* (F25) OSPI0_D2.GPIO0_5 */ /* SODIMM 60 */

>;

};

/* Verdin QSPI_1_IO3 as GPIO (conflict with Verdin QSPI_1 interface) */

pinctrl_qspi1_io3_gpio: main-gpio0-6-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x0018, PIN_INPUT, 7) /* (F24) OSPI0_D3.GPIO0_6 */ /* SODIMM 62 */

>;

};

/* Verdin QSPI_1 */

pinctrl_ospi0: main-ospi0-default-pins {

pinctrl-single,pins = <

AM62X_IOPAD(0x0000, PIN_OUTPUT, 0) /* (H24) OSPI0_CLK */ /* SODIMM 52 */

AM62X_IOPAD(0x002c, PIN_OUTPUT, 0) /* (F23) OSPI0_CSn0 */ /* SODIMM 54 */

AM62X_IOPAD(0x0030, PIN_OUTPUT, 0) /* (G21) OSPI0_CSn1 */ /* SODIMM 64 */

AM62X_IOPAD(0x000c, PIN_INPUT, 0) /* (E25) OSPI0_D0 */ /* SODIMM 56 */

AM62X_IOPAD(0x0010, PIN_INPUT, 0) /* (G24) OSPI0_D1 */ /* SODIMM 58 */

AM62X_IOPAD(0x0014, PIN_INPUT, 0) /* (F25) OSPI0_D2 */ /* SODIMM 60 */

AM62X_IOPAD(0x0018, PIN_INPUT, 0) /* (F24) OSPI0_D3 */ /* SODIMM 62 */

>;

};

/* Verdin QSPI_1 */

&ospi0 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ospi0>;

status = "disabled";

};

Thanks in advance!