I’m using gpioset to change gpio parameters, and it is working well, but I do not understand what I am seeing in registers.

When I start from a freshly rebooted system, I see SODIMM_217 listed as an input.

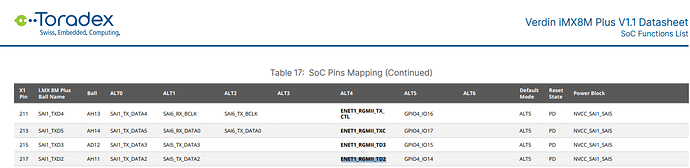

This is GPIO4_IO14.

Consulting the reference manual, the register IOMUXC_SW_MUX_CTL_PAD_SAI1_TXD2 should be set to 0x05 for this to be a GPIO. However, when I read that register (mapped at 0x30330180 from the ref manual) using devmem2, it shows:

root@verdin-imx8mp-15446091:~# devmem2 0x30330180 w

/dev/mem opened.

Memory mapped at address 0x7f93dd1000.

Read at address 0x30330180 (0x7f93dd1180): 0x00000004

I don’t understand why that address is set to 0x4 (ALT4, or ENET1_RGMII_TD2 mode) instead of 5.

I’m pretty sure I’m using devmem2 properly, for if I change the direction of that gpio, I can see the GPIO4 Direction register (0x30230004) change…

# pin is an output due to a previous gpioset

root@verdin-imx8mp-15446091:~# devmem2 0x30230004 w

/dev/mem opened.

Memory mapped at address 0x7f8c383000.

Read at address 0x30230004 (0x7f8c383004): 0x30484000

# Now set back to input with gpioget

root@verdin-imx8mp-15446091:~# gpioget SODIMM_217

# GPIO4 direction register changed in memory!

root@verdin-imx8mp-15446091:~# devmem2 0x30230004 w

/dev/mem opened.

Memory mapped at address 0x7f8ab9f000.

Read at address 0x30230004 (0x7f8ab9f004): 0x30480000

# However, this pin is still reporting it is not a GPIO...

root@verdin-imx8mp-15446091:~# devmem2 0x30330180 w

/dev/mem opened.

Memory mapped at address 0x7f93dd1000.

Read at address 0x30330180 (0x7f93dd1180): 0x00000004

This behavior does not happen on other gpio pins - their MUX controllers are properly set to 5. What am I missing?