Are there any instructions in this forum for how I can get a second PCIe root complex interface out of an Apalis iMX8 SOM?

I’ve managed to find some resources on this forum about how one can enable a two lane PCIe root complex in an Apalis module.

Currently working with the Apalis iMX8QM + Ixora breakout. I’m able to get both of my target PCIe endpoints working, one at a time, with the mini PCIe endpoint. What I need to do next is validate that I can speak to both of my endpoint devices at once with two separate PCIe root complexes.

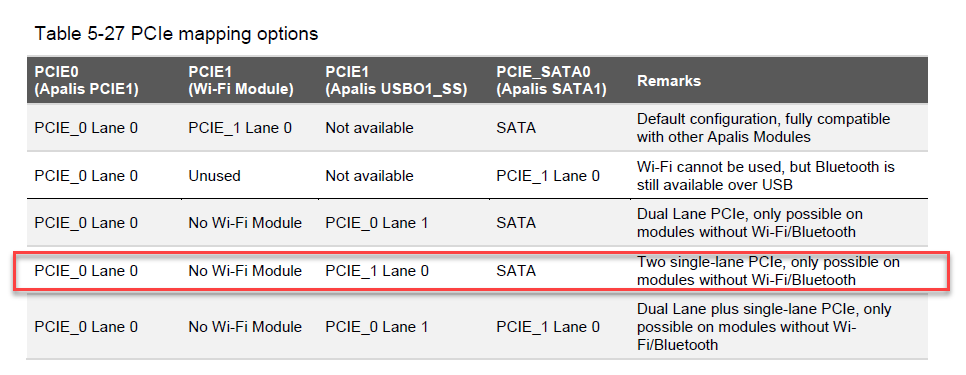

Based on prior experience bringing up second PCIe interfaces on other NXP chipsets, I think that would look something like this:

Hardware

- Getting custom SOM with no wifi module populated

- Add HCSL oscillator and/or fanout buffer to carrier board for reference clocks to both PCIe endpoints

- Add GPIO for Reset, CLK_REQ, and WAKE_L to each individual PCIe endpoint

Software

- Adding in device tree support for second PCIe interface

- Modify IOMUX to enable PCIe pins

- Disable SATA pins (could be same as IOMUX modifications)

- (Potentially) enable PCIe in Uboot (have worked with some NXP chipsets that require this)

I was hoping I might get some more specific guidance from the Toradex folks on what needs doing - and, of course, make sure that my request is feasible.