Hi @AhmedMobarez, how are you?

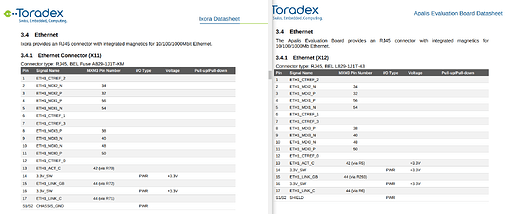

The pin naming is more related to the module itself and not to the carrier board. For instance, take the ethernet example:

Here you can see that the signal names are the same and also the pin numbering.

The main difference is that the Evaluation Board has a few more peripherals available and has all pins exposed so that you can do more testing and debugging in case you want to create your own carrier board.

I’m leaving the datasheets here:

Now talking specifically about the Cortex-M4, the pins are defined inside the pin_mux.c and pin_mux.h files from FreeRTOS. Let’s take the hello world from the core 0 as an example.

If we look at pin_mux.h inside SDK_2_9_0_MIMX8QM6xxxFF/boards/mekmimx8qm/demo_apps/hello_world/cm4_core0, we’ll see these defines:

/* M40_I2C0_SCL (number AM44), FTDI_M40_UART0_RX */

/* Routed pin properties */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_PERIPHERAL M40__UART0 /*!< Peripheral name */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_SIGNAL uart_rx /*!< Signal name */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_PIN_NAME M40_I2C0_SCL /*!< Routed pin name */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_PIN_FUNCTION_ID SC_P_M40_I2C0_SCL /*!< Pin function id */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_LABEL "FTDI_M40_UART0_RX" /*!< Label */

#define BOARD_INITPINS_FTDI_M40_UART0_RX_NAME "FTDI_M40_UART0_RX" /*!< Identifier */

Therefore, the RX is using the M40_I2C0_SCL pin for the UART debug. Now looking at the pin_mux.c file, we can see this function:

err = sc_pad_set_all(ipc, BOARD_INITPINS_FTDI_M40_UART0_RX_PIN_FUNCTION_ID, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SCL register modification value */

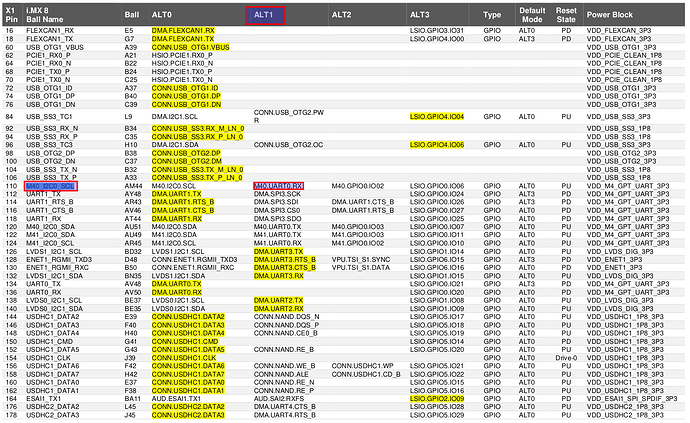

We can see that it is defining the pin M40_I2C0_SCL function 1U. Now looking at the Apalis iMX8 datasheet, we can search for this pin:

As you can see, function 1U (ALT1) is exactly M40.UART0.RX, which is the UART channel used by the Cortex-M4.

You can also see this is pin 110 from the edge connector. Now you can search if this pin is available on the carrier board. For the Apalis Evaluation Board, all pins are available, so you will be able to debug the Cortex-M4 core 0 using this pin. For the Ixora though, the 110 is not available, as I mentioned in this thread.

Finally, this is basically what you will need to do in order to develop your application with the Evaluation Board and deploy it to the Ixora board. You will need to search for these pins and make sure all of them are available. Here is the Ixora datasheet: https://docs.toradex.com/107020-ixora-v12-datasheet.pdf

For the Linux side, if you need to configure a pin (for example, changing a function or disabling it from Linux to use with the FreeRTOS), you will need to edit the device tree of the Ixora board.

Please, let me know if this is clear now, and feel free to ask any more questions you might have. We’re improving our documentation on the Cortex-M: High performance, low power Embedded Computing Systems | Toradex Developer Center. We expect to write more articles about it in the next weeks.

Best regards,

Hiago.