Today We made measurement of RMII interface with logic analyzer.

50 MHz ref. clock is sourced by Verdin.

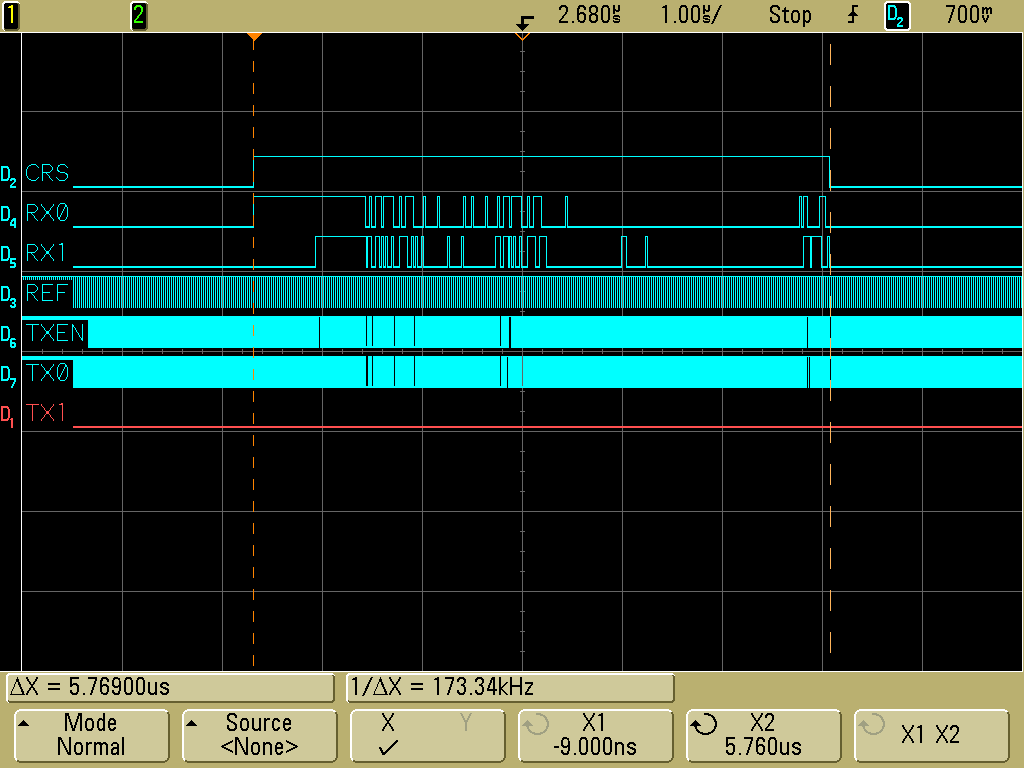

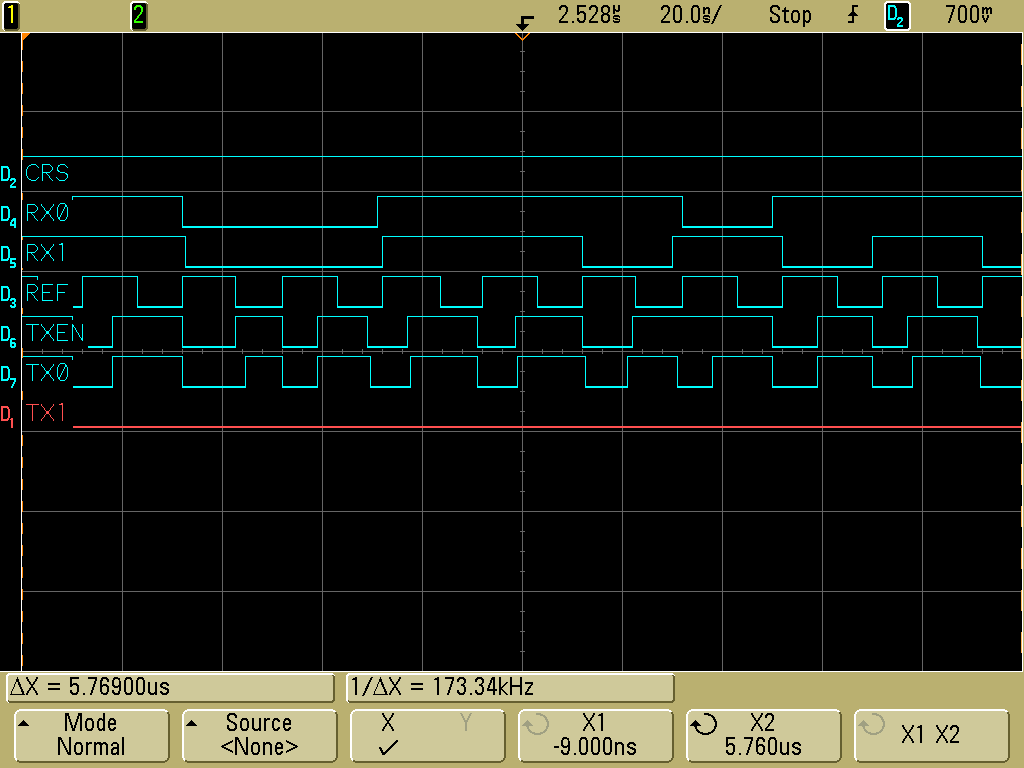

Ping attempt from external laptop connected to PORT 1:

The CRS, RX0 and RX1 signals from KSZ8873 to Verdin looks good from my point of view. The data signals are changed with rising edge of REF CLK and probably should be sampled by Verdin with falling edge of REF CLK. There is just one bit per clock cycle. There is something bad happenning on signals TXEN and TX0.

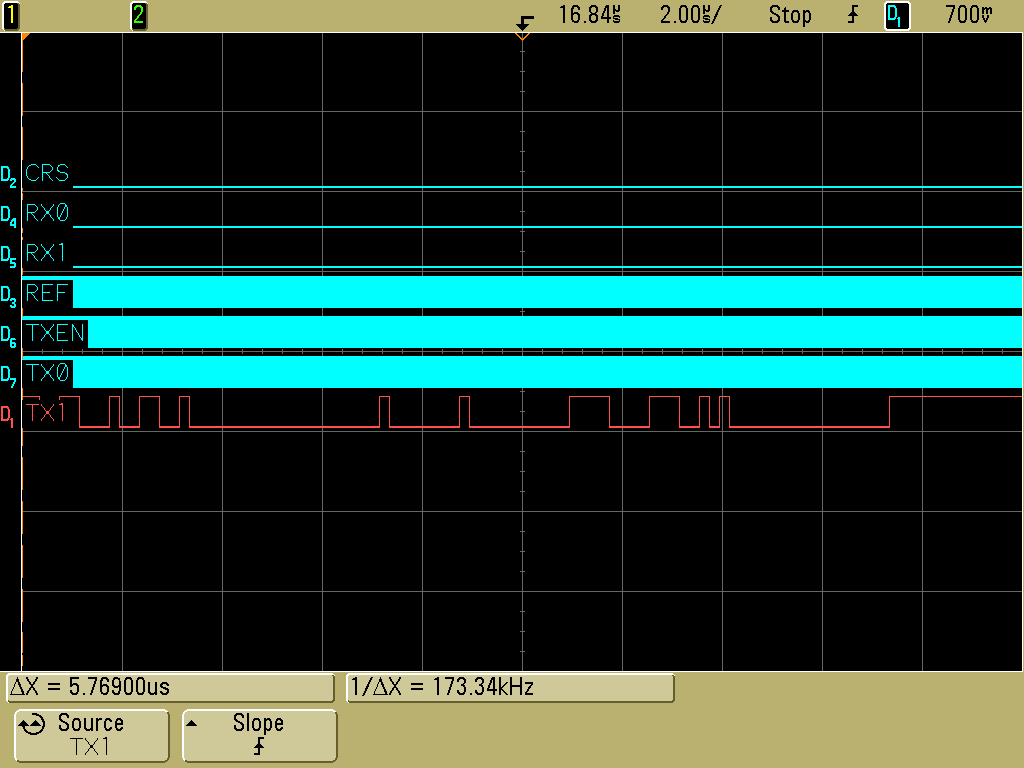

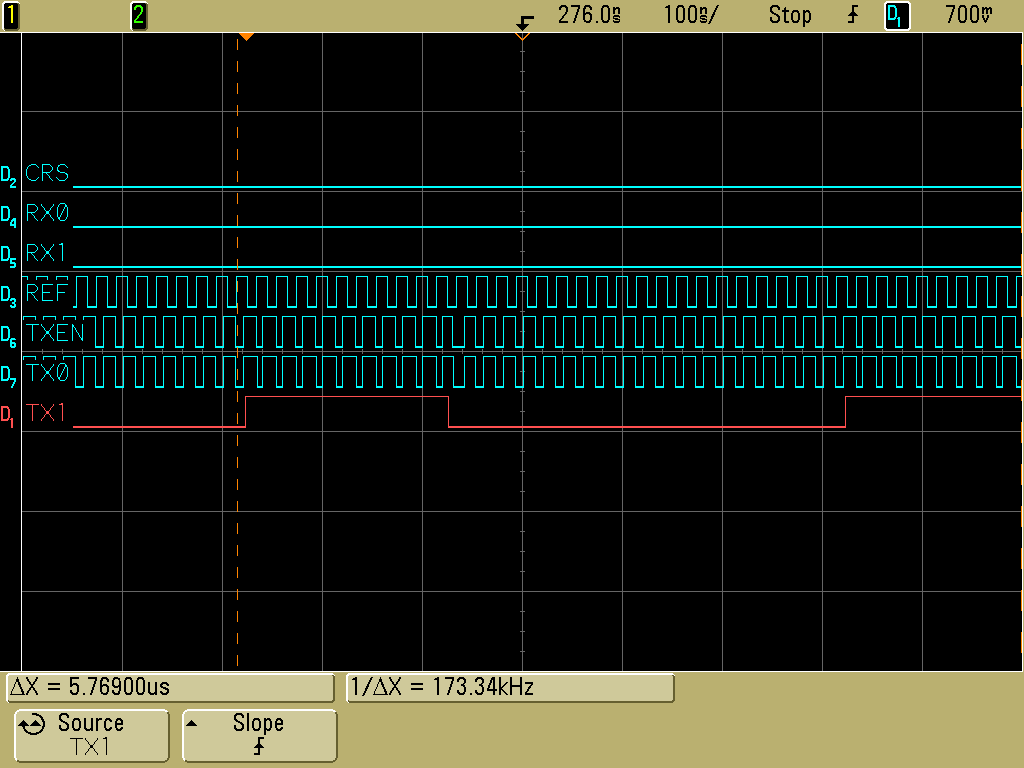

ARP attempt to get IP from external DHCP initiated from Verdin:

Something which looks like data appears on TX1, however there is “inverted 50 MHz clock with duty cycle > 0,5” on TX0 and TXEN, which definitely should not be there. The data on TX1 also has much lower frequency than REF CLK.

It seems Verdin ignores recieved data on CRS, RX0 and RX1, because there is no reply. Also the data on TXEN, TX0 and TX1 are totally different, then it should look like.