Hi, I need to use the PCIE_1_GPIO pins in the mallow carrier board and the verdin imx8mm as GPIO. Is it possible to use it, modifying the DTO?

Hi, I’m the Toradex AI Assistant.

I might make mistakes. Our support team will step in if needed. If I answered your question, please tick the “Solution” checkbox. For follow-up questions to me, please use @ToradexAI in your post.

Using PCIE_1_GPIO Pins as GPIO on Mallow Carrier Board

Yes, you can use the PCIE_1_GPIO pins on the Mallow carrier board as GPIO pins by creating a Device Tree Overlay (DTO). The Mallow carrier board provides several PCIE_1_GPIO pins that are connected to both the M.2 connector and the Secondary Extension Header (1)(2).

Available PCIE_1_GPIO Pins

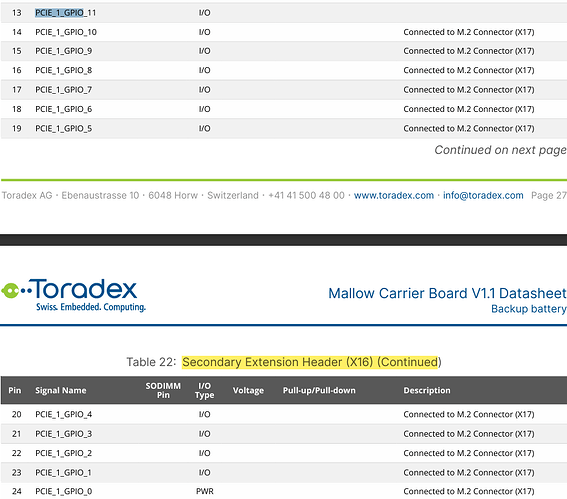

According to the Mallow Carrier Board V1.1 datasheet, the following PCIE_1_GPIO pins are available (1)(2):

- PCIE_1_GPIO_0 through PCIE_1_GPIO_11 - Connected to Secondary Extension Header (X16) (2)

- These pins are accessible on the M.2 Connector (X17) and routed to the Secondary Extension Header (1)(2)

Creating a Device Tree Overlay

To configure these pins as GPIO, you need to create a Device Tree Overlay that:

- Disables PCIe functionality if not needed

- Configures pin multiplexing to set the pins as GPIO

- Sets appropriate pin control parameters

Based on the community examples for similar GPIO configuration (3)(4), your overlay structure should include:

/dts-v1/;

/plugin/;

/ {

compatible = "toradex,verdin-imx8mm";

};

&iomuxc {

pinctrl_pcie_gpio: pcie_gpio_pins {

fsl,pins = <

/* Configure your specific PCIE_1_GPIO pins here */

/* Example format - adjust for your specific pins */

>;

};

};

Key Considerations

-

Pin Conflicts: Ensure the PCIE_1_GPIO pins you want to use are not conflicting with other enabled peripherals (5)

-

Device Tree Overlay Compilation: You’ll need to compile your overlay using Device Tree Compiler (DTC) or TorizonCore Builder (5)

-

Pin Control Settings: Use appropriate pad control register values for your GPIO requirements (3)

Deployment Process

- Write the overlay with correct pin multiplexing settings (5)

- Compile the overlay to generate the

.dtbofile (5) - Deploy the overlay to

/boot/dtb/overlays/directory (5) - Enable the overlay in your bootloader configuration (5)

The specific pin multiplexing values and GPIO numbers will depend on which exact PCIE_1_GPIO pins you want to use and how they’re mapped on the Verdin iMX8MM module.

Best regards, Toradex AI Assistant.

As shown in the Mallow schematic and the tables you provided, the mentioned GPIO pins on the Mallow X16 expansion header are connected only to the M.2 connector (X17). They are not routed to any Verdin pins, and no Device Tree modification can make them function as regular GPIOs.

The only way to utilize these pins as GPIO is by installing some kind of a GPIO expander to the X17 slot, controlled via either USB or PCIe.