I load Toradex Reference image Minimal to the hardware as below.

SOM: Verdin AM62 Solo Wifi-BT V1.1B

Carrier Board: Mallow V1.1B

My goal is to run a hello world program on CM4F core and R5F core but it seems that these 2 cores are not working yet.

I have enable device tree overlay “verdin-am62_spidev_overlay.dtbo” and it seems that Core M4F works.

How to make the R5F core works?

Thanks

Hi, I’m the Toradex AI Assistant. The Toradex Support team will follow up with you shortly!

Did you like my answer?

Hello,

To get the R5F core working on your Verdin AM62 SOM, please consider the following steps:

-

Device Tree Configuration: Ensure that the device tree overlay for the R5F core is correctly configured. You may need to create or modify an overlay, such as

verdin-am62_r5f_overlay.dtbo, to enable the R5F core. -

Bootloader Settings: Verify that the bootloader settings are configured to initialize the R5F core. This might involve specific configurations in U-Boot or another bootloader to enable secondary cores.

-

Firmware and Drivers: Check that the necessary firmware and drivers for the R5F core are included in your image. Ensure you have the latest updates or patches that might address R5F core initialization issues.

-

Debugging Output: Utilize debugging tools to capture output during the boot process. This can provide insights into why the R5F core is not initializing properly.

By following these steps, you should be able to troubleshoot and potentially resolve the initialization issue with the R5F core. If the problem persists, further investigation into your specific configuration and setup may be necessary.

Best regards,

Toradex AI Assistant

Please, also check if these links can help you solve your problem:

The device tree verdin-am62_r5f_overlay.dts is not existing.

Hi @ThinhNguyen!

In order to use the remote cores, you have to enable the overlay named verdin-am62_hmp_overlay.dtbo. This overlay reserves memory regions for the M4 and R5 cores.

In this other community topic, I described how you can build and run an example for the M4, and the step-by-step should be the same for R5. I recommend starting there.

Feel free to ask if you have any doubts or issues.

Best regards.

Lucas Fernandes Azeituno.

Hi lucas,

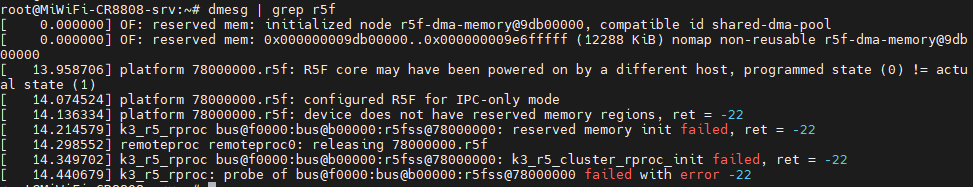

I enabled the verdin-am62_hmp_overlay.dtbo already, and got the error the same as the attached picture in my question.

The m4f core is up but the r5f core did not work.

Hi @ThinhNguyen!

I was mistaken, am62_hmp_overlay.dtbo reserves memory just for Cortex M4, but not for Cortex R5.

I’ll do some tests and try to get the Cortex R5 to work. In the meantime, I would recommend you search in TI’s documentation.

Best regards.

Lucas Azeituno.

HI @ThinhNguyen!

I tried to run an example on Cortex R5, and to do that I customized the device tree with the following overlay:

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/*

* Copyright 2024 Toradex

*/

// Arm Cortex-M4F processor core (MCU_M4FSS)

/dts-v1/;

/plugin/;

/ {

compatible = "toradex,verdin-am62";

};

&{/} {

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

rtos_ipc_memory_region: ipc-memories@9c800000 {

compatible = "shared-dma-pool";

reg = <0x00 0x9c800000 0x00 0x00300000>;

no-map;

};

mcu_m4fss_dma_memory_region: m4f-dma-memory@9cb00000 {

compatible = "shared-dma-pool";

reg = <0x00 0x9cb00000 0x00 0x100000>;

no-map;

};

mcu_m4fss_memory_region: m4f-memory@9cc00000 {

compatible = "shared-dma-pool";

reg = <0x00 0x9cc00000 0x00 0xe00000>;

no-map;

};

wkup_r5fss0_core0_memory_region: r5f-memory@9db00000 {

compatible = "shared-dma-pool";

reg = <0x00 0x9db00000 0x00 0x00c00000>;

no-map;

};

};

};

&mailbox0_cluster0 {

status = "okay";

mbox_m4_0: mbox-m4-0 {

ti,mbox-rx = <0 0 0>;

ti,mbox-tx = <1 0 0>;

};

mbox_r5_0: mbox-r5-0 {

ti,mbox-rx = <2 0 0>;

ti,mbox-tx = <3 0 0>;

};

};

&mcu_m4fss {

mboxes = <&mailbox0_cluster0 &mbox_m4_0>;

memory-region = <&mcu_m4fss_dma_memory_region>,

<&mcu_m4fss_memory_region>;

status = "okay";

};

&wkup_r5fss0_core0 {

firmware-name = "r5-firmware";

mboxes = <&mailbox0_cluster0 &mbox_r5_0>;

memory-region = <&wkup_r5fss0_core0_dma_memory_region>,

<&wkup_r5fss0_core0_memory_region>;

status = "okay";

};

&mcu_uart0 {

status = "reserved";

};

With this overlay, I could see the processor in the /sys/clas/remoteproc, but I couldn’t start/stop the core.

torizon@verdin-am62-15285103:~$ head /sys/class/remoteproc/remoteproc*/name

==> /sys/class/remoteproc/remoteproc0/name <==

5000000.m4fss

==> /sys/class/remoteproc/remoteproc1/name <==

78000000.r5f

==> /sys/class/remoteproc/remoteproc2/name <==

30074000.pru

==> /sys/class/remoteproc/remoteproc3/name <==

30078000.pru

As far as I read on the R5 driver, this processor enters on an “IPC-only” mode and gets attached (as you can see below), then I can’t control it (start/stop or load a new firmware). I’ve tried to start it in “remoteproc mode” in order to test if I could load a new firmware, but I could not achieve that. TI does not have long documentation about Cortex R5 (at least I didn’t find it), so I recommend you use Cortex M4 or go directly to TI’s forum and see if they can help you, since they have more expertise with this processor.

torizon@verdin-am62-15285103:~$ head /sys/class/remoteproc/remoteproc*/state

==> /sys/class/remoteproc/remoteproc0/state <==

running

==> /sys/class/remoteproc/remoteproc1/state <==

attached

==> /sys/class/remoteproc/remoteproc2/state <==

offline

==> /sys/class/remoteproc/remoteproc3/state <==

offline

Best regards.

Lucas Azeituno