Hello,

I am trying to make work LVDS dual channel with the Apalis IMX6 and the Apalis Evaluation Board but I am not able to get any video.

This is my UBoot vidargs

vidargs=mxc_hdmi.only_cea=1 video=mxcfb0:dev=ldb, video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M

And I also modified the device tree with the next:

--- a/arch/arm/boot/dts/imx6qdl-apalis.dtsi

+++ b/arch/arm/boot/dts/imx6qdl-apalis.dtsi

@@ -89,7 +89,7 @@

mxcfb1: fb@0 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "ldb";

- interface_pix_fmt = "RGB666";

+ interface_pix_fmt = "RGB24";

default_bpp = <16>;

int_clk = <0>;

late_init = <0>;

@@ -508,19 +508,32 @@

&ldb {

status = "okay";

-// split-mode;

-// dual-mode;

+ split-mode;

lvds-channel@0 {

reg = <0>;

fsl,data-mapping = "spwg"; /* "jeida"; */

- fsl,data-width = <18>;

+ fsl,data-width = <24>;

crtc = "ipu2-di1";

primary;

status = "okay";

display-timings {

- native-mode = <&timing_xga>;

+ native-mode = <&timing_widehd>;

+ timing_widehd: 1920x720 {

+ clock-frequency = <47500000>;

+ hactive = <1920>;

+ vactive = <720>;

+ hback-porch = <0>;

+ hfront-porch = <0>;

+ vback-porch = <0>;

+ vfront-porch = <0>;

+ hsync-len = <80>;

+ vsync-len = <40>;

+ /*hsync-active = <0>;

+ vsync-active = <0>;*/

+ pixelclk-active = <0>;

+ };

/* LDB-AM-800600LTNQW-A0H */

timing_svga: 800x600 {

clock-frequency = <55000000>;

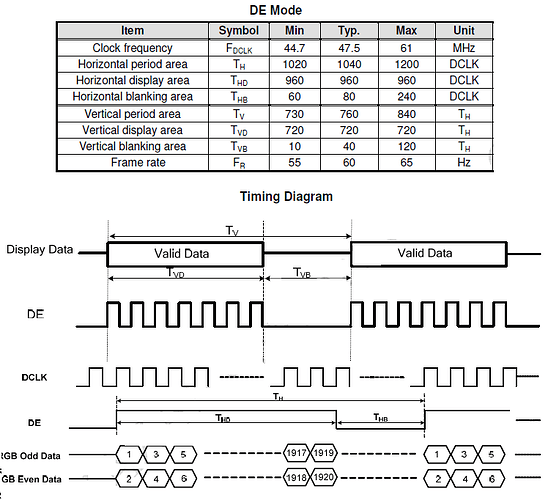

The timing of my TFT is:

Info of linux version:

root@apalis-imx6:~# uname -a

Linux apalis-imx6 4.9.87-2.8.4+g3bb6e3284a1b #1 SMP Fri Nov 30 03:50:06 UTC 2018 armv7l GNU/Linux

fbset info:

root@apalis-imx6:~# fbset

mode "1920x720-31"

# D: 47.501 MHz, H: 23.751 kHz, V: 31.251 Hz

geometry 1920 720 1920 720 16

timings 21052 0 0 0 0 80 40

rgba 5/11,6/5,5/0,0/0

endmode

Can you help me to review it and see If I am missing something?

Thanks