Hi Jaski,

I plan to use the i.MX7 Dual, my moduls were Revision D.

This module should work on my custom board (to be designed) but now I use the IRIS carrier board, but also have the Colibri development board V 3.2 here.

The target OS is WEC2013.

The BSP is the latest i.MX7 Version, also the SDK.

I need a SPI connection, Colibri is master and a SAM4N processor by Atmel is slave. According to hardware limitations of the SAM4N there is only byte transfer available at a max. speed of 15MHz.

The timing requirements for the data transfer in general dictates a very high speed, so with 15Mhz it is quite ok, at lower speeds the risk of data loss is higher.

On both sides ring buffers were used to decouple the time domains of the two systems.

System A: Powerd by SAM4N

System B: Powerd my AT-501 SoM, which should be replaced by Colibri i.MX7D.

A typical cycle:

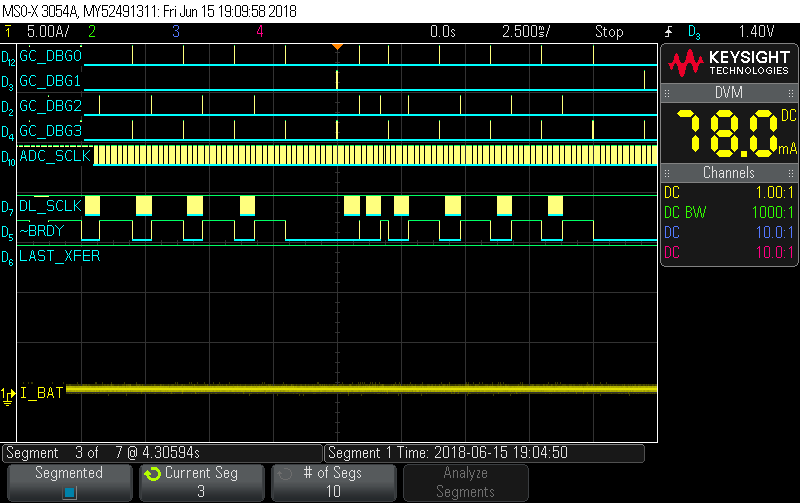

~BRDY, out of System A signals, that data is available for transfer.

DL_SCLK, output of System B is the SPI shiftclock (System B is master) so we can see the actual data transfer. Sometimes the OS (WEC2013) stops responding and so the ring buffers do their job to prevent data loss.

So I hope that the latency times on the i.MX7 are not longer than I see now (on the AT-501) and the transfer speed is close to 15MHz.

On my AT-501 ( and its BSP) I can fine tune the time span between ~CS goes low and SPI clock starts, in the moment I use a delay of 55ns. There is no chance to fine tune this (important) parameter on the i.MX7D & BSP, so there is just hope it will work out.

Currently I work on a port of the thin hardware related layer of my project, after finishing this work, I am able to do tests using real hardware.

Cause I am out of office from 10.9 to 24.9, I think, first results will be available in october.

With best regards

Gerhard