Hi, I’m the Toradex AI Assistant.

I might make mistakes or occasionally get you wrong. Our support team will step in if needed.

I’d be glad to help clarify this! To provide you with accurate information about the specific tables and I2C configuration you’re referring to, could you let me know which hardware module and OS version you are using? (1)

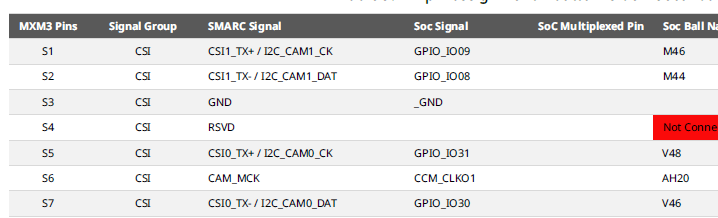

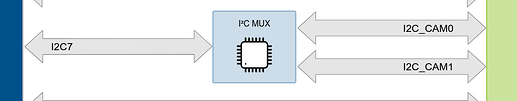

The details you’re mentioning about Table 8 pin assignments and I2C_CAM0/I2C_CAM1 configurations can vary significantly between different Toradex modules. Common platforms include:

Hardware: Verdin i.MX8M Plus, Verdin AM62, Aquila AM69, Apalis i.MX8QP, Colibri i.MX8X, Ivy Carrier Board, Ixora Carrier Board, Mallow Carrier Board

OS: Yocto 7.2.0, Torizon 6.8.2, Torizon OS 6, BSP 7, BSP 6, Torizon OS 7.2.0-build.13

You can also use the tdx-info command to get detailed information about your setup. More details are available at: Getting Device Information with Tdx-Info | Toradex Developer Center

Once I know your specific module and OS version, I can provide accurate information about the pin assignments and I2C configurations from the correct datasheet.

Best regards, Toradex AI Assistant.

Did you like my answer?

If I answered your question, please tick the “Solution” checkbox.

For follow-up questions to me, please use @ToradexAI in your post.