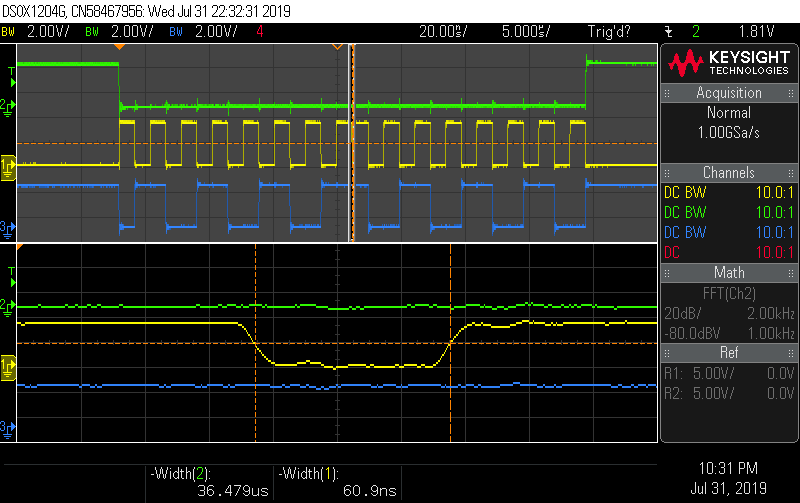

I have run a simple test to check the configuration of my SPI (as close to default as possible), and I’m worried by what I see on the signals, in particular SPI_CLK does not look healthy:

This shows a two byte transaction sending the string {0xFF, 0xAA}.

The top signal (green) is connected to SPI CS (pin 86), the middle signal (yellow) to SPI CLK (pin 88), and the bottom (blue) to SPI TXD (pin 92). I am troubled by the following two details, both affecting the clock:

- The falling edge of

CSand rising edge ofCLKare almost synchronous, and it looks as if the hold time for the first data bit is truncated to half a clock cycle. - There is a 60ns clock glitch between the first and second bytes. This is likely to cause my target hardware trouble. (Ok, not a “glitch” as such, but definitely a drastically truncated clock pulse.)

I’m hoping that I’ve simply misconfigured my SPI device, or perhaps am not talking to /dev/spidev1.0 correctly. My device tree is based on vf500-colibri-eval-v3.dts, with my customisations replacing vf-colibri-eval-v3.dtsi:

&dspi1 {

status = "okay";

spidev1: spidev@0 {

compatible = "toradex,evalspi";

reg = <0>;

spi-max-frequency = <10000000>; /* 10 MHz */

status = "okay";

};

};

and my test code is the following:

#include <stdint.h>

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

#include <sys/types.h>

#include <sys/stat.h>

#include <fcntl.h>

#include <sys/ioctl.h>

#include <linux/spi/spidev.h>

int main(int argc, char *argv[])

{

char data[] = { 0x55, 0xAA };

struct spi_ioc_transfer command = {

.tx_buf = (intptr_t) data,

.len = 2,

};

int dev = open("/dev/spidev1.0", O_RDWR);

ioctl(dev, SPI_IOC_MESSAGE(1), &command);

close(dev);

return 0;

}

P.S. I’ve realised that my data clock is only running at 400kHz! Is this the highest available speed under 10MHz for this device?