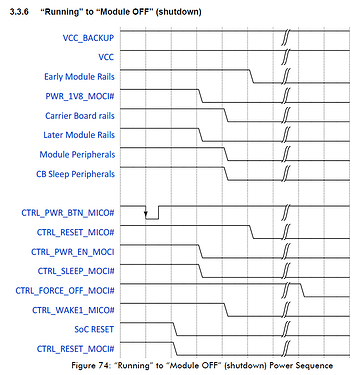

Working on a Verdin iMX8M Plus carrier board design. The design guide states in Section 3.3.10, “If the main module power rail is removed in any power state, the different power rails are shut down in a non-graceful order. This should not physically damage the module. However, the flash memory may get corrupted. Therefore, removing the VCC should be avoided if the system was not shut down properly in advance.”

The first question is, how risky is this? I am reaching out to our software engineer to confirm if we are booting from the Flash or from the uSD card. I expect if we are not booting from FLASH, then the damage from corruption would be minimal?

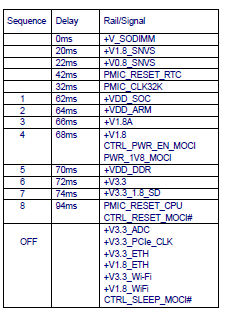

From the design guide, the family specifications, and the datasheet do not give timing diagrams for the power-down sequence. How long does a power-down sequence take?

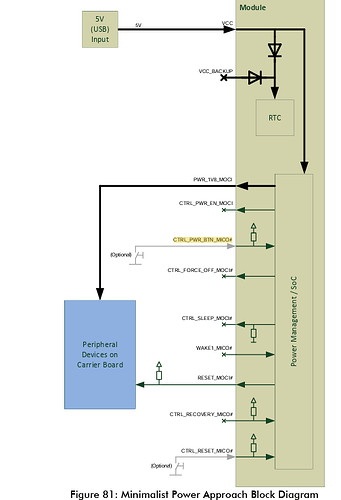

Does Toradex have a simple, recommended circuit (single IC ideally) that can help with this functionality?

I have designed complex soft-power-down circuits before for other designs. However, we really don’t want to be that complex. When the user hits the power-down switch, the system will turn off. If there is a small delay from when the power switch is switched off to when the power FET is actually turned off, that is okay. That is also easy to implement…but I don’t think that will work within the Toradex architecture.

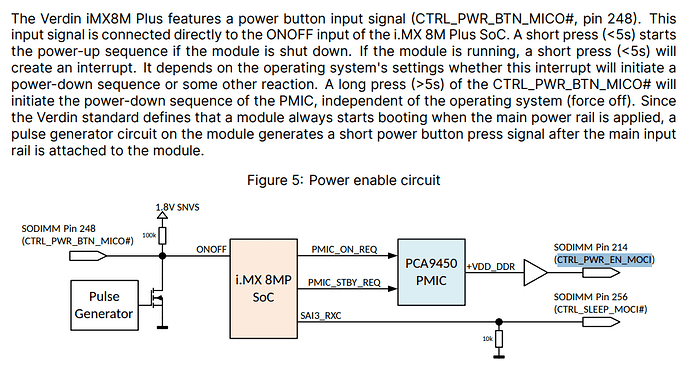

I would connect that ‘early’ detection signal to PWR_BTN_MICO# (in theory) to go from the Running State to the Off State. However, that signal would be low forever once the power switch was turned off. It seems the SOM would be waiting for it to go high to determine if it is a shut-down commend or a Force Off command?

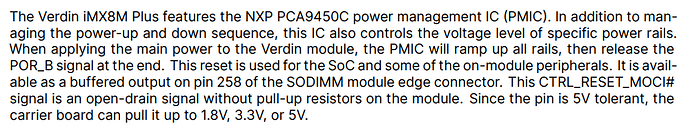

From the Power Management signal descriptions, it is not clear to me if the PWR_BTN_MICO# signal going high would turn on the module. However, on the State diagram, it looks like just VCC turning on is required?

This is the last aspect of our hardware design that has any questions and we are eager to get our carrier board on order. Thank you in advance for prompt assistance.

Best Regards,

Ben