Hi I am trying to use flex timer 1 in quadrature mode. I tried to do virtual memory mapping with a structure in order to initialize registers required for flextimer. The program looses connection with the device as soon as memory mapping is done. I am currently deploying the code using ethernet port and providing power supply using the mini usb port. Can somebody also tell me the other dependencies I need to address while using the flextimer to generated pwm?

My code is given below:

#include "stdafx.h"

#include "mapmem.h"

#include "clk_imx7.h"

#include "gpio_imx7.h"

#include <windows.h>

#define CCM_BASE_ADDR 0x30380000

#define CCM_CCGR128 0x30384800

#define CCM_TARGET_ROOT110 0x3038B700

typedef struct{

UINT32 FTM_SC;

UINT32 FTM_CNT;

UINT32 FTM_MOD;

UINT32 FTM_C0SC;

UINT32 FTM_C0V;

UINT32 FTM_C1SC;

UINT32 FTM_C1V;

UINT32 FTM_C2SC;

UINT32 FTM_C2V;

UINT32 FTM_C3SC;

UINT32 FTM_C3V;

UINT32 FTM_C4SC;

UINT32 FTM_C4V;

UINT32 FTM_C5SC;

UINT32 FTM_C5V;

UINT32 FTM_C6SC;

UINT32 FTM_C6V;

UINT32 FTM_C7SC;

UINT32 FTM_C7V;

UINT32 FTM_CNTIN;

UINT32 FTM_STATUS;

UINT32 FTM_MODE;

UINT32 FTM_SYNC;

UINT32 FTM_OUTINIT;

UINT32 FTM_OUTMASK;

UINT32 FTM_COMBINE;

UINT32 FTM_DEADTIME;

UINT32 FTM_EXTTRIG;

UINT32 FTM_POL;

UINT32 FTM_FMS;

UINT32 FTM_FILTER;

UINT32 FTM_QDCTRL;

UINT32 FTM_CONF;

UINT32 FTM_SYNCONF;

UINT32 FTM_INVCTRL;

UINT32 FTM_SWOCTRL;

UINT32 FTM_PWMLOAD;

}tFTM_REGS,*ptFTM_REGS;

BOOL FTM_ConfigureIos(HANDLE hGpio)

{

int i;

BOOL fSuccess = TRUE;

const uIo eimIo[] =

{

COLIBRI_PIN( 30), // flextimer1.PHA

COLIBRI_PIN( 67), // flextimer1.PHB

COLIBRI_PIN( 29) //flextimer1.CH[7]

};

/// The Flextimer functionality is on ALT 5 and the channel is on ALT 2.

for (i = 0; i < 2; i++) //_countof(eimIo)

fSuccess &= Imx7Gpio_SetConfigString(hGpio, eimIo[i], NULL, L"AltFn=5,dir=in", StoreVolatile);

fSuccess &= Imx7Gpio_SetConfigString(hGpio, eimIo[2], NULL, L"AltFn=2,dir=out", StoreVolatile);

return fSuccess;

}

int wmain(int argc, _TCHAR* argv[])

{

BOOL fSuccess = TRUE;

HANDLE hMap;

HANDLE hGpio;

ptFTM_REGS pFtm1Reg;

ptFTM_REGS pFtm1Reg;

UINT32 *tmp_ptr=NULL;

//volatile DWORD *clkRegs;

//volatile DWORD tmp;

//volatile DWORD *targetAddr;

char usr_input;

hMap=Map_Init();

hGpio = Imx7Gpio_Init(NULL);

fSuccess = FTM_ConfigureIos(hGpio);

fSuccess &= Imx7Gpio_Deinit(hGpio);

printf("%d\n",fSuccess);

pFtm1Reg=(ptFTM_REGS)Map_MapMemory(0x30640000,0x1000); //FTM1_SC is at 0x30640000

// FAILS AT THIS POINT *********************************************

//initialization is mentioned on pg 4197

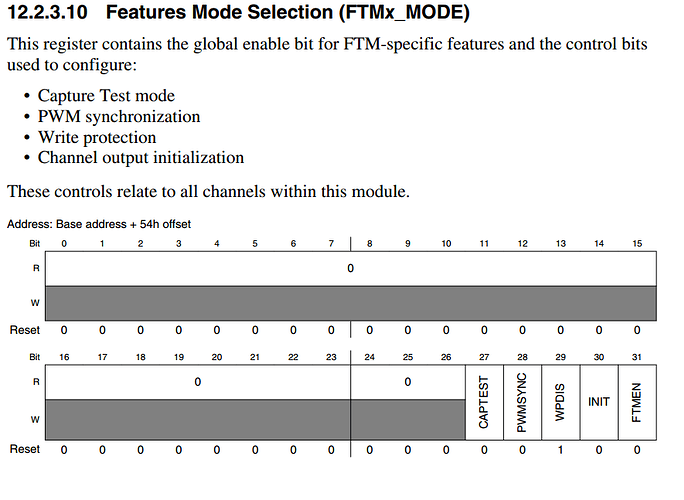

pFtm1Reg->FTM_MODE=0xE0000000;

pFtm1Reg->FTM_POL=0x00000000; //24 0 channel polarity is active high

pFtm1Reg->FTM_OUTMASK=0x00000000; //24 0 works normally

pFtm1Reg->FTM_MOD=0xFFFFFFFF; //16-32 ffff modulo value used in case of overflow

pFtm1Reg->FTM_CNTIN=0x00000000; //intial counter value

pFtm1Reg->FTM_SC=0x90000000; // 27-28 01 system clk

// 29-31 001 divide by 2

pFtm1Reg->FTM_C7SC=0x18000000; //channel status and control register

//26-27 01 mode selection output compare

//28-29 10 edge selection clear on match

pFtm1Reg->FTM_C7V=0x00100000;

pFtm1Reg->FTM_FMS=0x00000000; //25 0 write protection disabled

pFtm1Reg->FTM_SYNC=0x00000000; //used for PWM sychronization

pFtm1Reg->FTM_OUTINIT=0x00000000; //output initialization value for channels

pFtm1Reg->FTM_SYNCONF=0x00000000; //PWM synchronization configuration, SWOCTRL, INVCTRL

//and CNTIN registers synchronization

pFtm1Reg->FTM_COMBINE=0x00000000; //configure the synchronization, deadtime

//insertion, Dual Edge Capture mode, Complementary,

//and Combine mode for each pair of channels (n) and (n+1)

pFtm1Reg->FTM_CONF=0x00000000; //global time base for other FTM //unsure of use

pFtm1Reg->FTM_CNT=0x00000000; // initialize count

pFtm1Reg->FTM_QDCTRL=0xF0000000; //24 0 phase A input filter enable

//25 0 phase B filter input enable

//26 0 phase A input polarity

//27 0 phase B input polarity

//28 1 qadrature decoder mode

//29 1 FTM counter direction

//30 1 timer overflow direction

//31 1 quadrature decoder mode enable

pFtm1Reg->FTM_PWMLOAD=0x01800000; //22 1 load enable MOD, CNTIN, and CV

//24 1 channel 7 selected for compare match

while(TRUE){

scanf("%c",usr_input);

if(usr_input){

printf("\n encoder count: %zu",pFtm1Reg->FTM_CNT);

}

else if(usr_input=='Q' || usr_input=='q')

{

break;

}

}

return 0;

}