Hi,

I am running a bare metal code on M4 of my Verdin Mini, parallel to Linux. I use several interfaces from the M core, as you can see from my pinmux:

//DEBUG UART4

IOMUXC_SetPinMux(IOMUXC_UART4_RXD_UART4_RX, 0U);

IOMUXC_SetPinConfig(IOMUXC_UART4_RXD_UART4_RX,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_UART4_TXD_UART4_TX, 0U);

IOMUXC_SetPinConfig(IOMUXC_UART4_TXD_UART4_TX,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

//ECSPI2

IOMUXC_SetPinMux(IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK, 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI , 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI2_MISO_ECSPI2_MISO, 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI2_MISO_ECSPI2_MISO,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI2_SS0_GPIO5_IO13, 0U); // slave select pin as GPIO ! software controlled

IOMUXC_SetPinConfig(IOMUXC_ECSPI2_SS0_GPIO5_IO13,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

//FPGA Ready

IOMUXC_SetPinMux(IOMUXC_SAI3_TXFS_GPIO4_IO31 , 0U);

IOMUXC_SetPinConfig(IOMUXC_SAI3_TXFS_GPIO4_IO31 ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

//ECSPI1

IOMUXC_SetPinMux(IOMUXC_ECSPI1_SCLK_ECSPI1_SCLK , 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI1_SCLK_ECSPI1_SCLK ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI1_MOSI_ECSPI1_MOSI , 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI1_MOSI_ECSPI1_MOSI ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI1_MISO_ECSPI1_MISO , 0U);

IOMUXC_SetPinConfig(IOMUXC_ECSPI1_MISO_ECSPI1_MISO ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_ECSPI1_SS0_GPIO5_IO09 , 0U); // SPI1 CS MUX

IOMUXC_SetPinConfig(IOMUXC_ECSPI1_SS0_GPIO5_IO09 ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_NAND_CE3_B_GPIO3_IO04, 0U); // SPI1 CS DAC

IOMUXC_SetPinConfig(IOMUXC_NAND_CE3_B_GPIO3_IO04,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

IOMUXC_SetPinMux(IOMUXC_UART3_RXD_GPIO5_IO26 , 0U); // SPI1 CS BP

IOMUXC_SetPinConfig(IOMUXC_UART3_RXD_GPIO5_IO26 ,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

//SPI1 Reset, always high

IOMUXC_SetPinMux(IOMUXC_UART3_TXD_GPIO5_IO27, 0U);

IOMUXC_SetPinConfig(IOMUXC_UART3_TXD_GPIO5_IO27,

IOMUXC_SW_PAD_CTL_PAD_DSE(6U) |

IOMUXC_SW_PAD_CTL_PAD_FSEL(2U));

The problem is that when the linux is running, the Verdin suddenly restarts after some time (approx. a minute, not always the same).

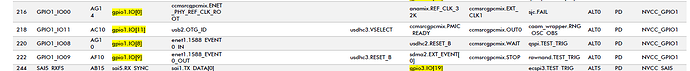

I think I managed to locate the problem at the FPGA_Ready pin that I’m using (GPIO4_IO31).

This pin is used as an input and it triggeres an interrupt handler that sets a flag fpgaReady = true, so that the SPI can read the data from the fpga slave.

Some additional code snippets for context:

#define FPGA_READY_GPIO_PIN 31U // fpga ready to send signal

#define FPGA_READY_GPIO GPIO4

void fpga_ready_enableInterrupt(){

GPIO_PortEnableInterrupts(FPGA_READY_GPIO, 1U << FPGA_READY_GPIO_PIN);

}

void GPIO4_Combined_16_31_IRQHandler(void)

{

fpgaReady = true;

GPIO_ClearPinsInterruptFlags(FPGA_READY_GPIO, 1U << FPGA_READY_GPIO_PIN);

}

bool is_FPGA_ready(void){

return fpgaReady;

}

The program doesn’t break when I turn off the linux in U-boot, so my guess is that I have some device tree interference. I created a custom overlay by slightly changing the overlay that was turned on by default, that is: verdin-imx8mm_lt8912_overlay.dts

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/*

* Copyright 2020-2021 Toradex

*/

// Verdin DSI to HDMI Adapter orderable at Toradex.

/dts-v1/;

/plugin/;

/ {

compatible = "toradex,verdin-imx8mm";

};

&gpu {

status = "okay";

};

&pwm1 {

status = "disabled";

};

/* Disable Verdin SPI */

&uart2 {

status = "disabled";

};

&uart3 {

status = "disabled";

};

&ecspi1 {

status = "disabled";

};

&ecspi2 {

status = "disabled";

};

I disabled the SPIs and UARTs that I’m using on the M side. In the case of the fpgaReady pin, it is the SODIMM 129 and the part of the uart2 by default, so I tought turning the UART2 off should solve this issue. It doesn’t ![]()

My additional question would also be: Do I have to disable all GPIO pins in the device tree that I’m using (e.g. three Chip Select pins for SPI1 that I use) on the M-Core and how do I do that?

Thanks in advance!