Dear all,

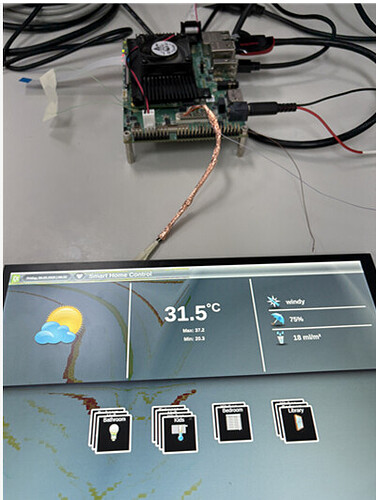

i’m working with the following configuration:

Apalis iMX8QM 4GB WB IT V1.1D

Ixora Carrier Board V 1.2A

DISTRO_VERSION = “6.8.2”

DISTRO_CODENAME = “krikstone”

10.1 I am trying to connect LCD(RGB666) to Ixora carrier board.

I want to connect LVDS1_B without using LVDS1_A (single mode)

I am writing device tree overlay:

&ldb2 {

status = "okay";

lvds-channel@0 {

status = "disabled"; // LVDS1_A OFF

};

lvds-channel@1 {

reg = <1>;

fsl,data-mapping = "spwg";

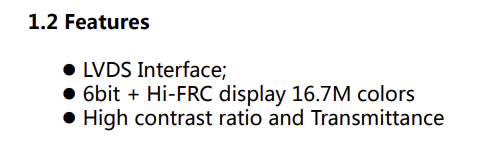

fsl,data-width = <18>;

status = "okay";

port@1 {

reg = <1>;

lvds1b_out: endpoint {

remote-endpoint = <&panel_lvds_in>;

};

};

};

};

&panel_lvds {

data-mapping = "jeida-18"; // jeida-18bit panel

height-mm = <136>;

width-mm = <217>;

status = "okay";

panel-timing {

clock-frequency = <72400000>;

de-active = <1>;

hactive = <1280>;

hback-porch = <88>;

hfront-porch = <72>;

hsync-active = <0>;

hsync-len = <40>;

pixelclk-active = <1>;

vactive = <800>;

vback-porch = <20>;

vfront-porch = <18>;

vsync-active = <0>;

vsync-len = <9>;

};

port {

panel_lvds_in: endpoint {

remote-endpoint = <&lvds1b_out>;

};

};

};

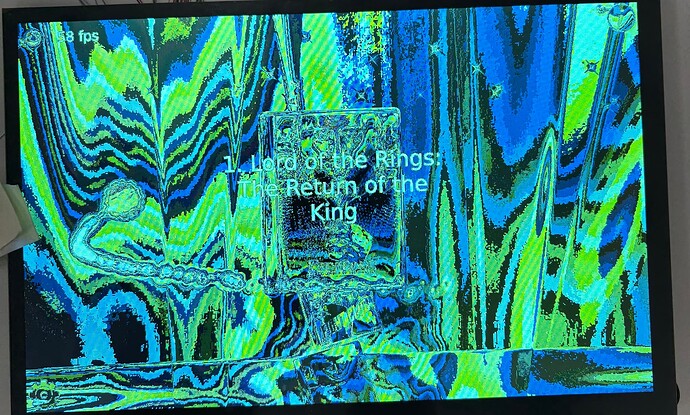

The colors on the LCD appear as follows:

Can you help me to solve this problem?

Best regards,

sjjin