Hi,

I tried to create overlay for my dual channel LVDS panel. Could someone please tell me if that overlay is correct?

&lvds_ti_sn65dsi84 {

ports {

#address-cells = <1>;

#size-cells = <0>;

port@2 {

reg = <2>;

lvds_out_panel_odd: endpoint {

remote-endpoint = <&panel_in_odd>;

};

};

port@3 {

reg = <3>;

lvds_out_panel_even: endpoint {

remote-endpoint = <&panel_in_even>;

};

};

};

};

&panel_lvds {

compatible = "panel-lvds";

backlight = <&backlight>;

data-mapping = "vesa-24"

height-mm = <110>;

width-mm = <292>;

status = "okay";

panel-timing {

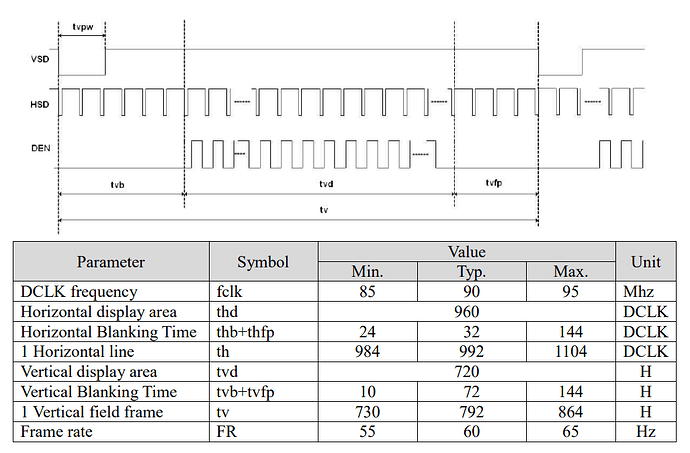

clock-frequency = <90000000>;

// datasheet says that hactive - 960

hactive = <1920>;

vactive = <720>;

hsync-len =< 0>;

vsync-len = <0>;

hfront-porch = <16>;

hback-porch = <16>;

vfront-porch = <46>;

vback-porch = <46>;

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dual-lvds-odd-pixels;

panel_in_odd: endpoint {

remote-endpoint = <&lvds_out_panel_odd>;

};

};

port@1 {

reg = <1>;

dual-lvds-even-pixels;

panel_in_even: endpoint {

remote-endpoint = <&lvds_out_panel_even>;

};

};

};

};

Timing characteristic from datasheet:

The base overlay what i was using was

display-lp156wf1_sn65dsi84_overlay.dtsi.

Im connecting that panel to imx8mp with

Dahlia carrier board through

Verdin DSI to LVDS Adapter.

Hello @Mhroczny ,

Have you tried the overlay yet? What did you observe? Do you have some pictures that is displayed with that overlay on the Display?

Best Regards,

Matthias

Thank you @matthias.tx for answer. The problem is the panel is not showing anything more like turned off. After adding overlay in /boot/overlay.txt im receiving

[ 13.790664] [drm:drm_crtc_commit_wait] *ERROR* flip_done timed out

[ 13.790686] [drm:drm_atomic_helper_wait_for_dependencies] *ERROR* [CRTC:33:crtc-0] commit wait timed out

[ 24.030699] [drm:drm_crtc_commit_wait] *ERROR* flip_done timed out

[ 24.030722] [drm:drm_atomic_helper_wait_for_dependencies] *ERROR* [CONNECTOR:38:LVDS-1] commit wait timed out

[ 34.270681] [drm:drm_crtc_commit_wait] *ERROR* flip_done timed out

[ 34.270703] [drm:drm_atomic_helper_wait_for_dependencies] *ERROR* [PLANE:31:plane-0] commit wait timed out

and

[ 209.197191] sn65dsi83 3-002c: failed to lock PLL, ret=-6

Running # find /sys/devices -name "edid":

/sys/devices/platform/display-subsystem/drm/card1/card1-HDMI-A-1/edid

/sys/devices/platform/display-subsystem/drm/card1/card1-LVDS-1/edid

Force a connector state with echo on > /sys/class/drm/card1-LVDS-1/status has no result

Dear @Mhroczny

We had a look at your device tree overlay and it should more looks like something like this:

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/*

* Copyright 2020-2022 Toradex

*/

// Verdin DSI to LVDS Adapter orderable at Toradex.

/dts-v1/;

/plugin/;

/ {

compatible = "toradex,verdin-imx8mp";

};

#include "verdin-imx8_mipi-dsi-to-sn65dsi84.dtsi"

&lvds_ti_sn65dsi84 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@2 {

reg = <2>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>;

};

};

};

};

&panel_lvds {

compatible = "panel-lvds";

backlight = <&backlight>;

data-mapping = "vesa-24";

height-mm = <136>;

width-mm = <217>;

status = "okay";

panel-timing {

clock-frequency = <85000000 90000000 95000000>;

// datasheet says that hactive - 960

hactive = <960>;

vactive = <720>;

hsync-len =< 1>;

vsync-len = <1>;

hfront-porch = <10 16 50>;

hback-porch = <10 16 50>;

vfront-porch = <10 36 50>;

vback-porch = <10 36 50>;

de-active = <1>; /* try 1 and 0 */

pixelclk-active = <1>; /* try 1 and 0 */

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>;

};

};

};

&backlight {

status = "okay";

};

&gpu_2d {

status = "okay";

};

&gpu_3d {

status = "okay";

};

/* LCDIF to MIPI-DSI */

&lcdif1 {

status = "okay";

};

&mix_gpu_ml {

status = "okay";

};

&ml_vipsi {

status = "okay";

};

&vpu_g1 {

status = "okay";

};

&vpu_g2 {

status = "okay";

};

&vpu_vc8000e {

status = "okay";

};

&vpu_v4l2 {

status = "okay";

};

If this doesn’t improve anything, can you share the following with us?

i2cdetect -r -y 0

i2cdetect -r -y 1

i2cdetect -r -y 2

i2cdetect -r -y 3

Further, can you also share the following:

cat /sys/class/drm/card1-LVDS-1/modes

And this output:

modetest

Regards,

Stefan

Thank you for your reply @stefan_e.tx

After setting panel timing - horizontal and vertical settings like in display-lp156wf1_sn65dsi84_overlay.dtsi the panel worked like a charm. Then I recived exact values of hsync-len and vsync-len from panel supplier and it worked for me.

The mistake was setting 0 for hsync and vsync length.

Setting two port nodes was also crucial in my case - 2 channel LVDS. Putting your DTO suggestion result was half horizontal screen streached to full screen.

Your suggestion also is solving the issue by setting panel timing in right way (non zero hsync and vsync).

Thank you very much for help and support