Hello Toradex team,

I hope you are all doing great and you had a good time at Embedded World !

Hardware:

- SoM Verdin IMX8M Plus Quad 4GB WB IT v1.1A

- Heatsink Verdin Industrial Heatsink Type 1 V1.0B

- Dual-Band Wi-Fi/Bluetooth PCB Antenna 100mm V1.0A

- Custom Carrier Board based on Verdin

tdx-info:

Software summary

------------------------------------------------------------

Bootloader: U-Boot

Kernel version: 5.15.129-6.5.0+git.6f8fd49366db #1-TorizonCore SMP PREEMPT Fri Dec 22 11:15:52 UTC 2023

Kernel command line: root=LABEL=otaroot rootfstype=ext4 quiet logo.nologo vt.global_cursor_default=0 plymouth.ignore-serial-consoles splash fbcon=map:3 ostree=/ostree/boot.1/torizon/d9775fd5577822ec4e9d6473745ca17c46edd81fc5d56864931253b6cc6414eb/0

Distro name: NAME="TorizonCore"

Distro version: VERSION_ID=6.5.0-build.8

Distro variant: VARIANT="Docker"

Hostname: verdin-imx8mp-14777575

------------------------------------------------------------

Hardware info

------------------------------------------------------------

HW model: iMX8M Plus on *** Board

Toradex version: 0058 V1.1A

Serial number: 14777XXX

Processor arch: aarch64

------------------------------------------------------------

Images tested:

- torizon-core-docker-verdin-imx8mp-Tezi_6.5.0+build.8.tar (STABLE Release)

Guest OS:

- macOS (M1 Pro ARM64)

- Linux ubuntu (VM x86_64)

Issue:

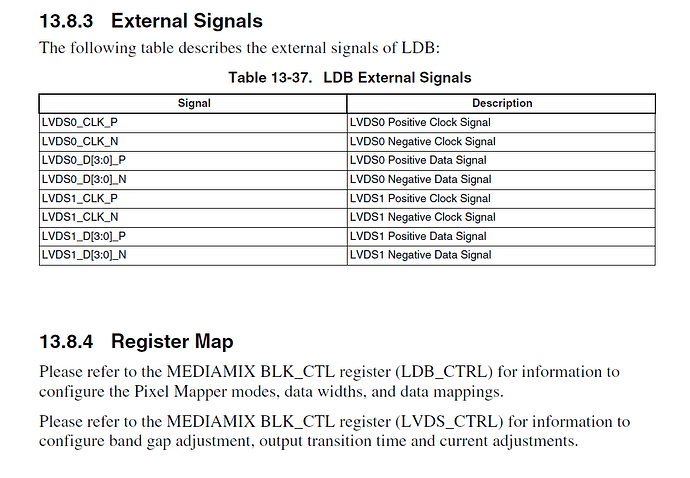

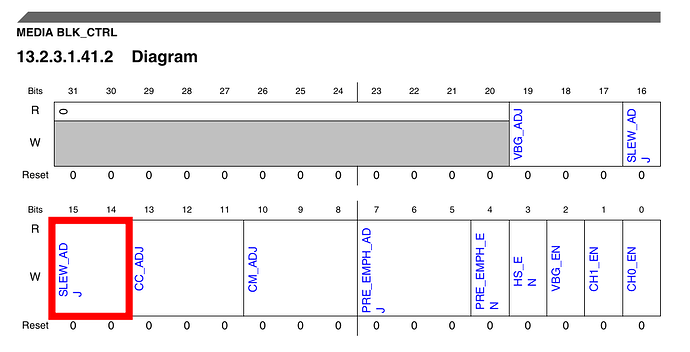

We are trying to pass the EMI test and it seems that our LVDS display is the one blocking us to pass the test. The CLK is to fast and we want to tweak it by changing the MEDIA BLK_CTRL.

Based on the i.MX 8M Plus Applications Processor Reference Manual that I downloaded on NXP, those values can be modified but I don’t understand how those can be achieve in my dts.

I have found the definition of media_blk_ctrl in the imx8mp.dtsi and this is used as clock by lcdif2 used by LVDS display. So far so good. But the clock seems off in the register used:

...

clocks = <&media_blk_ctrl IMX8MP_CLK_MEDIA_BLK_CTRL_LCDIF2_PIXEL>,

<&media_blk_ctrl IMX8MP_CLK_MEDIA_BLK_CTRL_LCDIF2_AXI>,

<&media_blk_ctrl IMX8MP_CLK_MEDIA_BLK_CTRL_LCDIF2_APB>;

...

So my question is, do you have an idea how I can change the value of those clocks to reduce the spike in the signal ? This is beyond my small expertise in device-tree, so if you can guide me a bit that would be very nice !

Thank you in advance.

Best regards,

M