Hello,

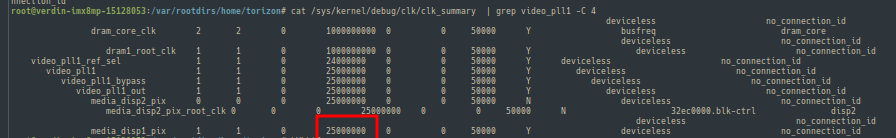

(On Torizon OS 6.8.0)

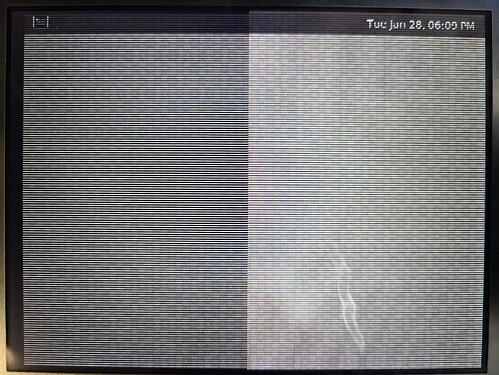

I am using a slightly modified version of the DSI to LVDS adapter, basically all that’s been changed is the removal of the backlight and touchscreen related functionality and adding a JAE connector to attach to twisted pairs to our display. I have configured the DTS for the timing of the new LVDS display, but it has visual glitching where the left half of the display seems to be jittering around left/right a few pixels on a line by line basis. The first line seems to jitter more, up to half the screen of pixels. In the below screenshot, the top line seems to have shifted ~4 pixels.

My display has these timings in the DTS:

panel-timing {

clock-frequency = <24400000 25200000 27300000>; // Min/typ/max clk in hz

de-active = <1>; // active high display enable in datasheet

hactive = <640 640 640>; // horizontal resolution

hback-porch = <50 53 70>; // Min/typ/max #clock

hfront-porch = <50 53 70>; // Min/typ/max #clock

hsync-len = <50 53 70>; // Min/typ/max #clock

pixelclk-active = <1>; // positive edge

vactive = <480 480 480>; // vertical resolution

vback-porch = <12 15 18>; // Min/typ/max #clock

vfront-porch = <12 15 18>; // Min/typ/max #clock

vsync-len = <12 15 18>; // Min/typ/max #clock

};

It is a 18 bit display.

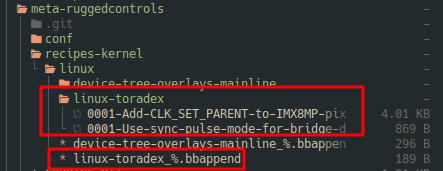

The display does not use HS and VS LVDS signals, and relies on the DE signal. It does not provide separate front porch / back porch / sync length values and only gives the totals. When I distribute these times equally amongst the timings in the DTS overlay, the issue occurs. I have tried specifying individual values rather than max/min/typ, I’ve tried messing with polarity of clock/de, and I’ve also tried using values from the RGB parallel version of this display which specifies the actual pulse width / front/back porch numbers. All of these either don’t work at all or have the jitter seen above.

From the datasheet:

- CLK Frequency (min/typ./max): 24.4/25.2/27.3 MHz

- Horizontal

- Display Data: 640 Clks

- Total Cycle Time (min/typ./max): 688/800/850 Clks

- Vertical:

- Display Data: 480 H

- Total Cycle Time (min/typ./max): 516/525/535 H

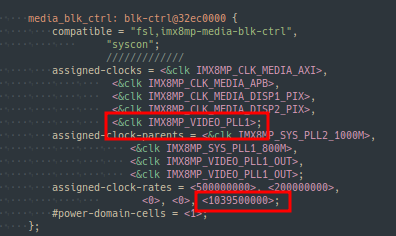

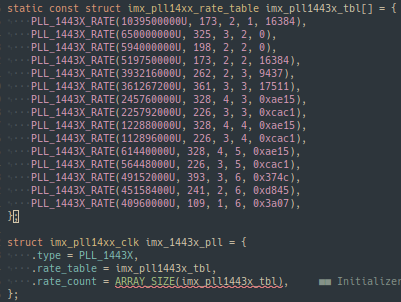

Could there be an issue with the DTSses such that the pixel buffers aren’t being filled fast enough? Or could there be an issue with jitter due to spread spectrum? I’d very much appreciate any assistance here diagnosing the issues.

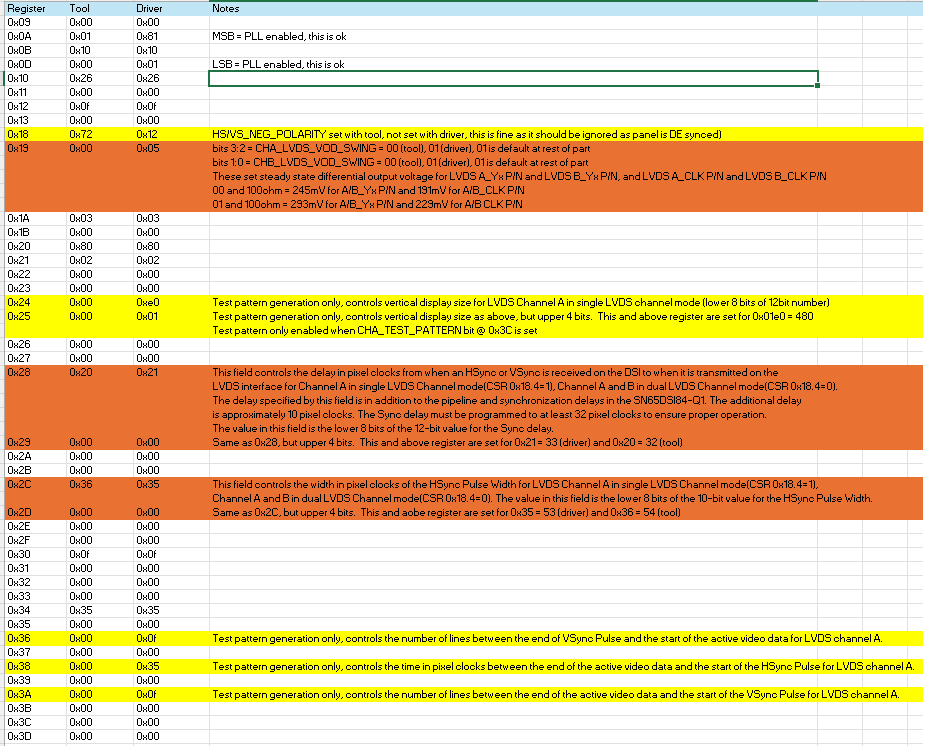

I have also played with i2cset/i2cget to use values from the DSI tuner from TI, but the differences in values don’t seem to change the issue.

However, putting the DSI to LVDS bridge in the test pattern mode shows a proper test pattern with no jitter - so it is likely that the LVDS portion (cables, display, configuration) works but the DSI portion to the bridge and the corresponding DTS/DSI configuration is broken.