Hi,

On the Apalis IMX8QM with a custom board, the interface is never up.

Here the dts :

&fec2 {

pinctrl-names = “default”, “sleep”;

pinctrl-0 = <&pinctrl_fec2>;

pinctrl-1 = <&pinctrl_fec2_sleep>;fsl,magic-packet; fsl,mii-exclusive; phy-supply = <®_ext_rgmii>; phy-handle = <ðphy1>; phy-mode = "rgmii-id"; status = "okay"; mdio { #address-cells = <1>; #size-cells = <0>; ethphy1: ethernet-phy@7 { compatible = "ethernet-phy-ieee802.3-c22"; interrupt-parent = <&lsio_gpio2>; interrupts = <22 IRQ_TYPE_LEVEL_LOW>; micrel,led-mode = <0>; reset-assert-us = <10000>; reset-deassert-us = <50000>; reset-gpios = <&lsio_gpio2 23 GPIO_ACTIVE_LOW>; reset-names = "phy-reset"; reg = <7>; }; }; };pinctrl_fec2: fec2grp {

fsl,pins = <

IMX8QM_COMP_CTL_GPIO_1V8_3V3_ENET_ENETA_PAD 0x000014a0

IMX8QM_ENET1_MDC_CONN_ENET1_MDC 0x06000020

IMX8QM_ENET1_MDIO_CONN_ENET1_MDIO 0x06000060

IMX8QM_ENET1_RGMII_TX_CTL_CONN_ENET1_RGMII_TX_CTL 0x06000020

IMX8QM_ENET1_RGMII_TXC_CONN_ENET1_RGMII_TXC 0x06000020

IMX8QM_ENET1_RGMII_TXD0_CONN_ENET1_RGMII_TXD0 0x06000020

IMX8QM_ENET1_RGMII_TXD1_CONN_ENET1_RGMII_TXD1 0x06000020

IMX8QM_ENET1_RGMII_TXD2_CONN_ENET1_RGMII_TXD2 0x06000020

IMX8QM_ENET1_RGMII_TXD3_CONN_ENET1_RGMII_TXD3 0x06000020

IMX8QM_ENET1_RGMII_RXC_CONN_ENET1_RGMII_RXC 0x06000020

IMX8QM_ENET1_RGMII_RX_CTL_CONN_ENET1_RGMII_RX_CTL 0x06000020

IMX8QM_ENET1_RGMII_RXD0_CONN_ENET1_RGMII_RXD0 0x06000020

IMX8QM_ENET1_RGMII_RXD1_CONN_ENET1_RGMII_RXD1 0x06000020

IMX8QM_ENET1_RGMII_RXD2_CONN_ENET1_RGMII_RXD2 0x06000020

IMX8QM_ENET1_RGMII_RXD3_CONN_ENET1_RGMII_RXD3 0x06000020

IMX8QM_ENET1_REFCLK_125M_25M_CONN_ENET1_REFCLK_125M_25M 0x06000020

IMX8QM_USDHC1_DATA6_LSIO_GPIO5_IO21 0x04000060;

};pinctrl_fec2_sleep: fec2-sleepgrp {

fsl,pins = <

IMX8QM_COMP_CTL_GPIO_1V8_3V3_ENET_ENETA_PAD 0x000014a0IMX8QM_ENET1_MDC_LSIO_GPIO4_IO18 0x04000040 IMX8QM_ENET1_MDIO_LSIO_GPIO4_IO17 0x04000040 IMX8QM_ENET1_RGMII_TX_CTL_LSIO_GPIO6_IO11 0x04000040 IMX8QM_ENET1_RGMII_TXC_LSIO_GPIO6_IO10 0x04000040 IMX8QM_ENET1_RGMII_TXD0_LSIO_GPIO6_IO12 0x04000040 IMX8QM_ENET1_RGMII_TXD1_LSIO_GPIO6_IO13 0x04000040 IMX8QM_ENET1_RGMII_TXD2_LSIO_GPIO6_IO14 0x04000040 IMX8QM_ENET1_RGMII_TXD3_LSIO_GPIO6_IO15 0x04000040 IMX8QM_ENET1_RGMII_RXC_LSIO_GPIO6_IO16 0x04000040 IMX8QM_ENET1_RGMII_RX_CTL_LSIO_GPIO6_IO17 0x04000040 IMX8QM_ENET1_RGMII_RXD0_LSIO_GPIO6_IO18 0x04000040 IMX8QM_ENET1_RGMII_RXD1_LSIO_GPIO6_IO19 0x04000040 IMX8QM_ENET1_RGMII_RXD2_LSIO_GPIO6_IO20 0x04000040 IMX8QM_ENET1_RGMII_RXD3_LSIO_GPIO6_IO21 0x04000040 /* IMX8QM_ENET1_REFCLK_125M_25M_LSIO_GPIO4_IO16 0x04000040 */ /* not wired on ECU */ /* IMX8QM_LVDS1_GPIO01_LSIO_GPIO1_IO11 0x06000020 */ IMX8QM_USDHC1_DATA6_LSIO_GPIO5_IO21 0x04000040 >;};

[ 7.406371] Microchip KSZ9131 Gigabit PHY 5b050000.ethernet-2:07: attached PHY driver (mii_bus:phy_addr=5b050000.ethernet-2:07, irq=280)

# ethtool eth1

Settings for eth1:

Supported ports: [ TP MII ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: Yes

Supported FEC modes: Not reported

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Advertised pause frame use: Symmetric

Advertised auto-negotiation: Yes

Advertised FEC modes: Not reported

Speed: Unknown!

Duplex: Unknown! (255)

Port: Twisted Pair

PHYAD: 7

Transceiver: external

Auto-negotiation: on

MDI-X: Unknown

Supports Wake-on: g

Wake-on: d

Link detected: no

I have tried to force the phy at 100M, without success

# ethtool -s eth1 speed 100 duplex full autoneg off

The interface never up even with this command.

3: eth1: <NO-CARRIER,BROADCAST,MULTICAST,UP> mtu 1500 qdisc mq qlen 1000

link/ether 00:14:2d:7d:ef:a2 brd ff:ff:ff:ff:ff:ff

inet 192.168.1.1/24 scope global eth1

valid_lft forever preferred_lft forever

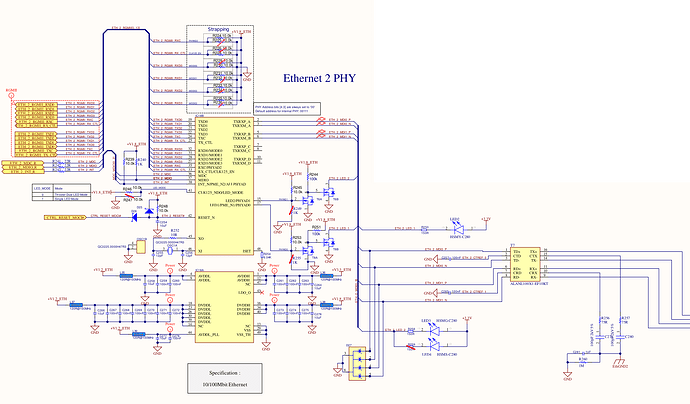

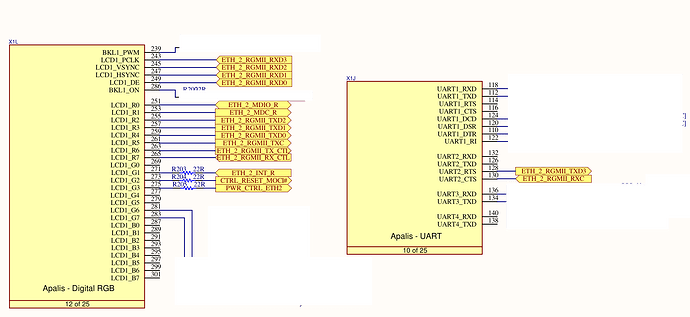

On the PCB, the KSZ9131 is routed in the 10/100 configuration. Only the ports A and B in connected to the transceiver.

A crystal @25MHz is connected to on the XI/XO pins and it works great.

I see the clock on the mdc pin when I set up the interface and I see something trying to discuss with the address 7. My ksz if configured with the address 7.

The reset pin is high.

Any idea ?