Hello,

We are encountering issues while setting up the Verdin Dev Board v1.1f (Verdin imx8mp) with the RVT50HQLNWC00-B display (Riverdi) through the Toradex DSI-to-LVDS Adapter (rev 1.1).

The display works correctly on our custom board, where it is connected directly to the LVDS output of the imx8mp (after applying kernel driver changes outlined here). These changes require the use of Yocto, but we would like to avoid it in production in order to maintain full compatibility with the Torizon environment.

We have created a device tree overlay for the RVT50HQLNWC00-B 5-inch display based on files provided by Toradex: display-lt170410_sn65dsi84_overlay.dtsi and verdin-imx8mp_dsi-to-lvds_panel-cap-touch-10inch-lvds_overlay.dts.

- display-rvt50hqlnwc00b_sn65dsi84_overlay.dtsi:

// Verdin DSI to LVDS Adapter with connected RVT50HQLNWC00-B display (5 inch) with a

// resolution of 800x480 pixel.

&lvds_ti_sn65dsi84 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@2 {

reg = <2>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>;

};

};

};

};

&panel_lvds {

compatible = "panel-lvds";

backlight = <&backlight>;

data-mapping = "vesa-24"; // jeida-24

height-mm = <108>;

width-mm = <65>;

status = "okay";

panel-timing {

clock-frequency = <25000000>;

de-active = <1>;

hactive = <800>;

hback-porch = <48>;

hfront-porch = <48>;

hsync-len = <8>;

pixelclk-active = <1>; /* positive edge */

vactive = <480>;

vback-porch = <12>;

vfront-porch = <12>;

vsync-len = <8>;

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>;

};

};

};

- verdin-imx8mp_dsi-to-lvds_panel-cap-touch-5inch-lvds_overlay.dts:

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/*

* Copyright 2020-2022 Toradex

*/

// Verdin DSI to LVDS Adapter orderable at Toradex.

/dts-v1/;

/plugin/;

/ {

compatible = "toradex,verdin-imx8mp";

};

#include "verdin-imx8_mipi-dsi-to-sn65dsi84.dtsi"

#include "display-rvt50hqlnwc00b_sn65dsi84_overlay.dtsi"

&atmel_mxt_ts {

status = "okay";

};

&backlight {

status = "okay";

};

&gpu_2d {

status = "okay";

};

&gpu_3d {

status = "okay";

};

/* LCDIF to MIPI-DSI */

&lcdif1 {

status = "okay";

};

&mix_gpu_ml {

status = "okay";

};

&ml_vipsi {

status = "okay";

};

&vpu_g1 {

status = "okay";

};

&vpu_g2 {

status = "okay";

};

&vpu_vc8000e {

status = "okay";

};

&vpu_v4l2 {

status = "okay";

};

®_dsi_lvds {

/* Verdin CTRL_SLEEP_MOCI# (SODIMM 256) */

gpio = <&gpio4 29 GPIO_ACTIVE_HIGH>;

};

- tcbuild.yaml:

input:

easy-installer:

local: images/torizon-core-docker-verdin-imx8mp-Tezi_6.8.1+build.25.tar

customization:

device-tree:

include-dirs:

- linux/include/

custom: linux/arch/arm64/boot/dts/freescale/imx8mp-verdin-nonwifi-dev.dts

overlays:

add:

- device-trees/overlays/verdin-imx8mp_dsi-to-lvds_panel-cap-touch-5inch-lvds_overlay.dts

output:

easy-installer:

local: build/torizon-core-docker-verdin-imx8mp-Tezi_6.8.1+build.25.tar.CUSTOM

Below are the issues we are facing with the overlays:

| Setting | Observed Behavior |

|---|---|

| data-mapping: vesa-24 | Display does not work correctly (image: vesa24-selb-8bit-display.jpg) |

| data-mapping: jeida-24 | Colors on display appear dimmed (image: jeida24-selb-8bit-display.jpg) |

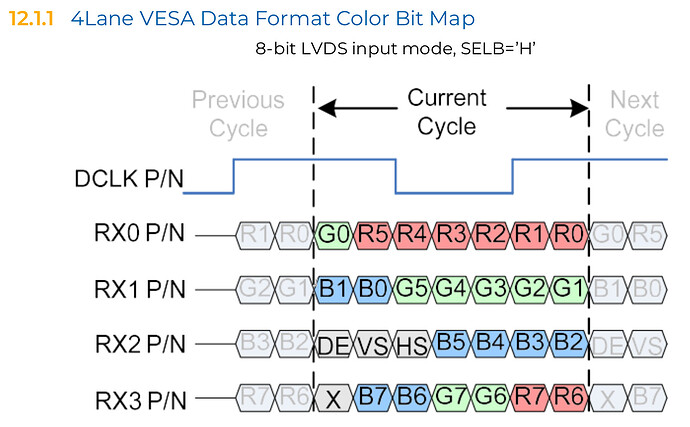

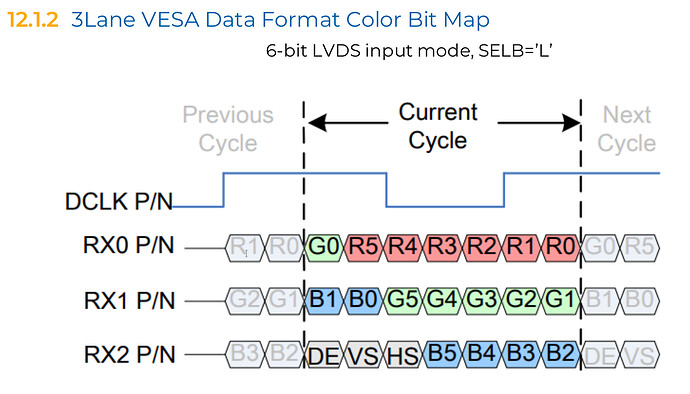

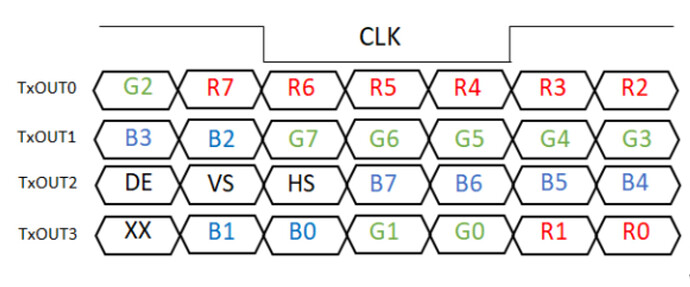

According to the display’s datasheet, the correct data-mapping is VESA. It is confusing that we need to set Jeida, which is not appropriate. On our custom board, the native LVDS display works fine with the nominal VESA-24 settings. What could be causing this issue?

Additionally, we are facing another problem with the color output. When the display is set to 8-bit input (SELB pin tied to High), the colors appear dimmed. However, when we switch it to 6-bit mode (SELB pin tied to Low), the colors look correct (image: jeida24-selb-6bit-display.jpg). How can we properly configure the 8-bit mode in the device tree while using the DSI-to-LVDS bridge?