Hello,

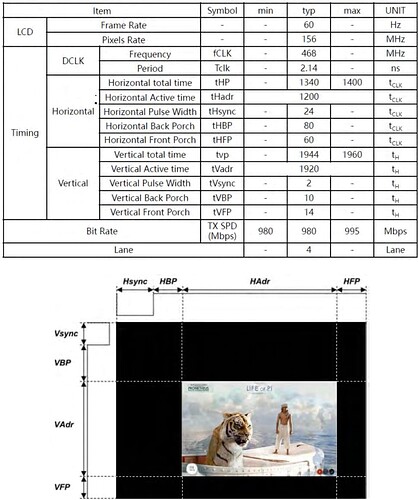

we are using a Verdin iMX8MM Q 2GB WB IT with a 1920x1200 MIPI-DSI panel with the following timings and patch:

diff --git a/Documentation/devicetree/bindings/display/panel/panel-simple-dsi.yaml b/Documentation/devicetree/bindings/display/panel/panel-simple-dsi.yaml

index fbd71669248f..3f2b9f17f49c 100644

--- a/Documentation/devicetree/bindings/display/panel/panel-simple-dsi.yaml

+++ b/Documentation/devicetree/bindings/display/panel/panel-simple-dsi.yaml

@@ -43,6 +43,8 @@ properties:

- lg,acx467akm-7

# LG Corporation 7" WXGA TFT LCD panel

- lg,ld070wx3-sl01

+ # Multi-Inno Technology Co.,Ltd 10.1" WUXGA TFT LCD panel

+ - mit,mi1010aqt-1

# One Stop Displays OSD101T2587-53TS 10.1" 1920x1200 panel

- osddisplays,osd101t2587-53ts

# Panasonic 10" WUXGA TFT LCD panel

diff --git a/drivers/gpu/drm/panel/panel-simple.c b/drivers/gpu/drm/panel/panel-simple.c

index 23767dcb75bc..ebab8c4aef9d 100644

--- a/drivers/gpu/drm/panel/panel-simple.c

+++ b/drivers/gpu/drm/panel/panel-simple.c

@@ -482,12 +482,6 @@ static int panel_simple_prepare(struct drm_panel *panel)

if (p->prepared)

return 0;

- ret = pm_runtime_get_sync(panel->dev);

- if (ret < 0) {

- pm_runtime_put_autosuspend(panel->dev);

- return ret;

- }

-

p->prepared = true;

return 0;

@@ -5163,6 +5157,35 @@ static const struct panel_desc_dsi lg_lh500wx1_sd03 = {

.format = MIPI_DSI_FMT_RGB888,

.lanes = 4,

};

+

+static const struct drm_display_mode mit_mi1010aqt_1_mode = {

+ .clock = 159420,

+ .hdisplay = 1200,

+ .hsync_start = 1200 + 80,

+ .hsync_end = 1200 + 80 + 24,

+ .htotal = 1200 + 80 + 24 + 60,

+ .vdisplay = 1920,

+ .vsync_start = 1920 + 16,

+ .vsync_end = 1920 + 16 + 4,

+ .vtotal = 1920 + 16 + 4 + 16,

+};

+

+static const struct panel_desc_dsi mit_mi1010aqt_1 = {

+ .desc = {

+ .modes = &mit_mi1010aqt_1_mode,

+ .num_modes = 1,

+ .bpc = 8,

+ .size = {

+ .width = 136,

+ .height = 217,

+ },

+ .connector_type = DRM_MODE_CONNECTOR_DSI,

+ },

+ .flags = MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_SYNC_PULSE |

+ MIPI_DSI_CLOCK_NON_CONTINUOUS,

+ .format = MIPI_DSI_FMT_RGB888,

+ .lanes = 4,

+};

static const struct drm_display_mode panasonic_vvx10f004b00_mode = {

.clock = 157200,

@@ -5265,6 +5288,9 @@ static const struct of_device_id dsi_of_match[] = {

}, {

.compatible = "lg,lh500wx1-sd03",

.data = &lg_lh500wx1_sd03

+ }, {

+ .compatible = "mit,mi1010aqt-1",

+ .data = &mit_mi1010aqt_1

}, {

.compatible = "panasonic,vvx10f004b00",

.data = &panasonic_vvx10f004b00

The demo weston-simple-egl -f is running with 56 fps. To reduce power consumption, I want to limit the frame rate to 30 fps.

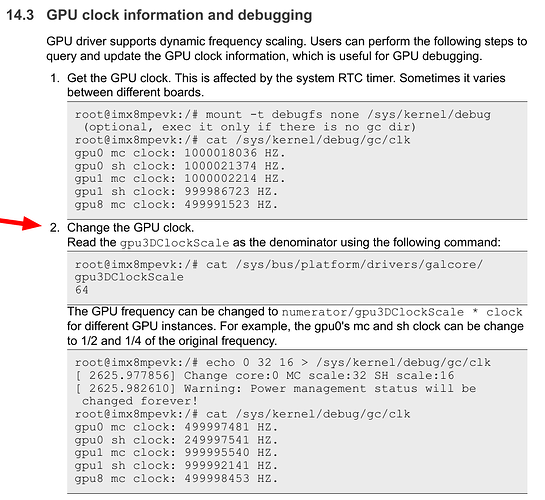

What is the right place to achieve this? Do I have to halve the pixel rate of the panel in the struct drm_display_mode? Or do I have to modify the clock of the gpu in the devicetree?

Best regards,

Markus