Hello,

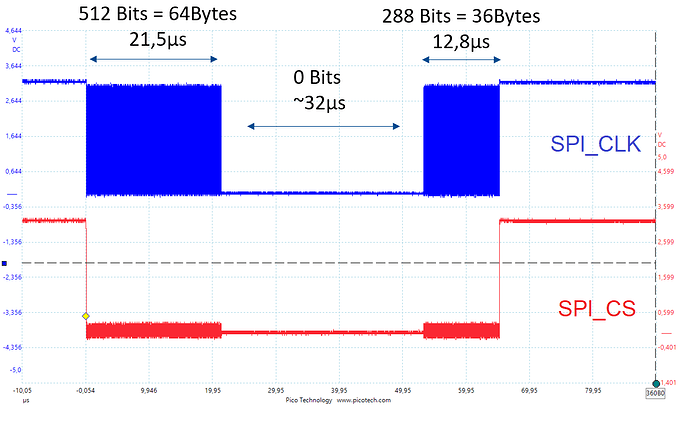

While sending 100 Bytes through SPI, a relatively big latency emerges after bursting 512bits (64Bytes) of data, then the SPI driver continue sending the rest bytes (36Bytes) as shown in picture:

How can increase the burst size (or how can i remove this latency)?

Oscilloscope:

SPI C code:

#define SPI_CLK_SPEED 20 * 1000000

#define SPI_BITS 8

#define SPI_DELAY 0

static const char *device = "/dev/spidev0.0";

struct spi_ioc_transfer tr;

int fd_spi;

uint8_t default_tx[100] ;

uint8_t default_rx[ARRAY_SIZE(default_tx)] = {0, };

void transfer(int fd,struct spi_ioc_transfer* tr, uint8_t const *tx, uint8_t const *rx, size_t len)

{

int ret;

tr->tx_buf = (unsigned long)tx;

tr->rx_buf = (unsigned long)rx;

tr->len = len;

ret = ioctl(fd, SPI_IOC_MESSAGE(1), tr);

if (ret < 1)

{

pabort("can't send spi message");

exit(1);

}

}

int SPI_init( const char *dev,struct spi_ioc_transfer *tr,uint32_t mode,uint8_t bits,uint32_t speed,uint16_t delay)

{

int spiFD,ret;

tr->delay_usecs = delay;

tr->speed_hz = speed;

tr->bits_per_word = bits;

if (mode & SPI_TX_QUAD)

tr->tx_nbits = 4;

else if (mode & SPI_TX_DUAL)

tr->tx_nbits = 2;

if (mode & SPI_RX_QUAD)

tr->rx_nbits = 4;

else if (mode & SPI_RX_DUAL)

tr->rx_nbits = 2;

if (!(mode & SPI_LOOP)) {

if (mode & (SPI_TX_QUAD | SPI_TX_DUAL))

tr->rx_buf = 0;

else if (mode & (SPI_RX_QUAD | SPI_RX_DUAL))

tr->tx_buf = 0;

}

spiFD = open(dev, O_RDWR);

if (spiFD < 0)

pabort("can't open device");

// spi mode

ret = ioctl(spiFD, SPI_IOC_WR_MODE32, &mode);

if (ret == -1)

pabort("can't set spi mode");

ret = ioctl(spiFD, SPI_IOC_RD_MODE32, &mode);

if (ret == -1)

pabort("can't get spi mode");

//bits per word

ret = ioctl(spiFD, SPI_IOC_WR_BITS_PER_WORD, &bits);

if (ret == -1)

pabort("can't set bits per word");

ret = ioctl(spiFD, SPI_IOC_RD_BITS_PER_WORD, &bits);

if (ret == -1)

pabort("can't get bits per word");

// max speed hz

ret = ioctl(spiFD, SPI_IOC_WR_MAX_SPEED_HZ, &speed);

if (ret == -1)

pabort("can't set max speed hz");

ret = ioctl(spiFD, SPI_IOC_RD_MAX_SPEED_HZ, &speed);

if (ret == -1)

pabort("can't get max speed hz");

printf("spi mode: 0x%x\n", mode);

printf("bits per word: %d\n", bits);

printf("max speed: %d Hz (%d KHz)\n", speed, speed/1000);

return (spiFD);

}

int main()

{

fd_spi = SPI_init(device,&tr,SPI_MODE,SPI_BITS,SPI_CLK_SPEED,SPI_DELAY);

fd_spi01 =

while(1)

{

usleep(200);

transfer(fd_spi,&tr, default_tx, default_rx, 100);

}

}