Hi,

I make a carrier board for Apalis IMX6 and I have 5 questions :

1 - What can I do with TS_ signals if not used? I think I do not connect them, but I want to be sure.

2 - I use the vga video signal but i do not have a monitor, so no DDC. Can i just left the I2C2(DDC) to pull up and use an internal configuration?

3 - I want to output PAL and NTSC format on this VGA. Any problem to do that?

Apalis iMX6 # setenv vidargs video=mxcfb0:dev=vga,(NTSC or PAL),if=RGB24 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M

Apalis iMX6 # saveenv

4 - I use the VGA output for my design. Could you give me the internal VGA DAC reference of my IMX6?

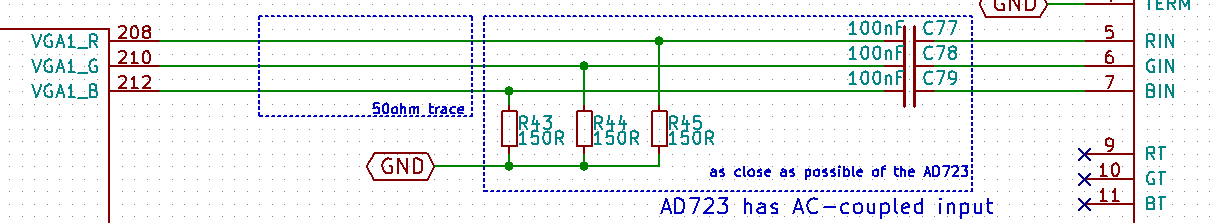

5 - If i want a 75ohm input AC-coupled. Is that the correct schematic?

Regards