Hi, I’m the Toradex AI Assistant.

I might make mistakes or occasionally get you wrong. Our support team will step in if needed.

I understand you’re experiencing delays in SPI communication with your FPGA on the Colibri iMX6 running WEC 2013. Let me help you identify potential solutions to reduce these timing delays.

SPI Performance Considerations

Based on the Toradex documentation, the i.MX6 SPI controllers (ECSPI) operate at up to 23 Mbps and provide several features that can impact timing performance (1)(2):

- 32-bit x 64 deep FIFO (RX and TX) (1)(2)

- Master/Slave configurable (1)(2)

- Simultaneous receive and transmit (1)(2)

- DMA support (1)(2)

Potential Solutions for Reducing SPI Delays

1. Use DMA-Based SPI Library

For better performance with larger data transfers, consider using the SPI via DMA Library (SPIDMALib) (3). This library is specifically designed to manage SPI interfaces via DMA and can provide better timing characteristics (3).

The SPIDMALib supports up to 5 SPI ports on Colibri modules and includes both DMA-based and polling mode functions (3). For data packets smaller than the FIFO (32 frames), the polling mode functions are recommended as they require less overhead and provide shorter latencies (3).

2. Check Your Pin Configuration

Your current pin configuration uses:

- Clock: Pin 153

- MOSI: Pin 155

- MISO: Pin 157

- CS: Pin 159

According to the Colibri iMX6 datasheet, these correspond to the standard Colibri SPI interface (1)(2):

- Pin 88 (SSPSCLK): Serial Clock (1)(2)

- Pin 92 (SSPTXD): Master Output, Slave Input (1)(2)

- Pin 90 (SSPRXD): Master Input, Slave Output (1)(2)

- Pin 86 (SSPFRM): Slave Select (1)(2)

3. Optimize SPI Mode and Timing

The i.MX6 supports four different SPI modes (1)(2):

- Mode 0: Clock positive polarity, data latched on positive edge

- Mode 1: Clock positive polarity, data latched on negative edge

- Mode 2: Clock negative polarity, data latched on positive edge

- Mode 3: Clock negative polarity, data latched on negative edge

Ensure your FPGA and the SPI controller are configured for the same mode to minimize setup and hold time issues.

4. Consider Library Version

The SPIDMALib documentation indicates that Library revision V5.0 and higher automatically handles frequency management between SpiInit and SpiDeinit, which can improve performance (3).

Recommendations

- Upgrade to SPIDMALib: Consider migrating to the DMA-based SPI library for better performance characteristics

- Use Polling Mode: For small transfers like your 4-byte example, polling mode functions may provide better latency than DMA

- Verify Pin Assignments: Ensure your pin configuration matches the standard Colibri SPI interface

- Check Library Version: Use the latest available version of the SPI libraries

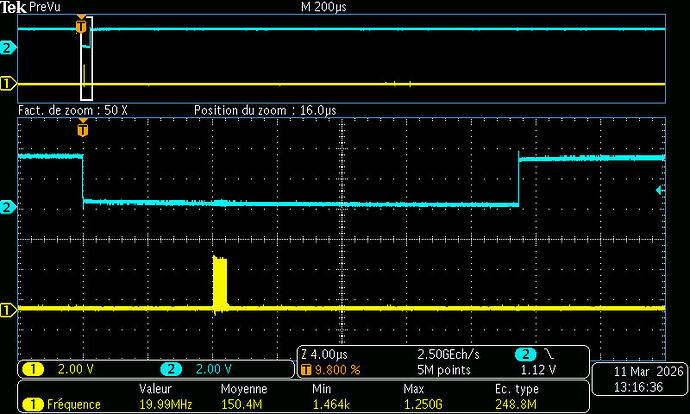

The 9µs delay you’re observing before data transmission could be related to the library’s internal setup overhead or timing characteristics of the specific SPI implementation you’re using.

Best regards, Toradex AI Assistant.

Did you like my answer?

If I answered your question, please tick the “Solution” checkbox.

For follow-up questions to me, please use @ToradexAI in your post.