hello!!

The image we are using is a custom one, based on yocto thud.

Yes, we have changed some drivers, device tree, etc. in order to make our old 5" TFT display work, like many other devices.

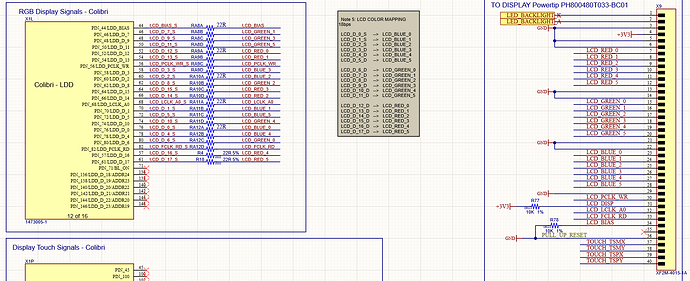

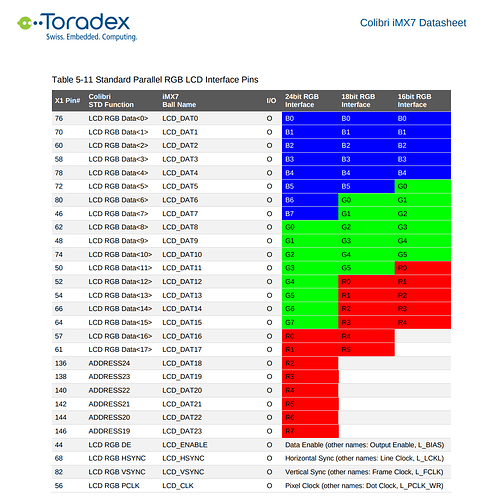

The SOM we are using is a Colibri IMX7D 1GB V1.1A.

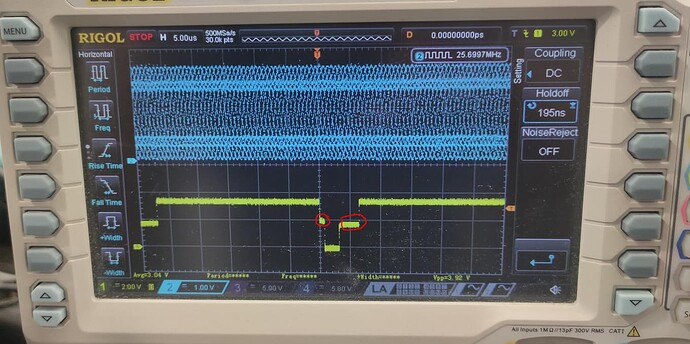

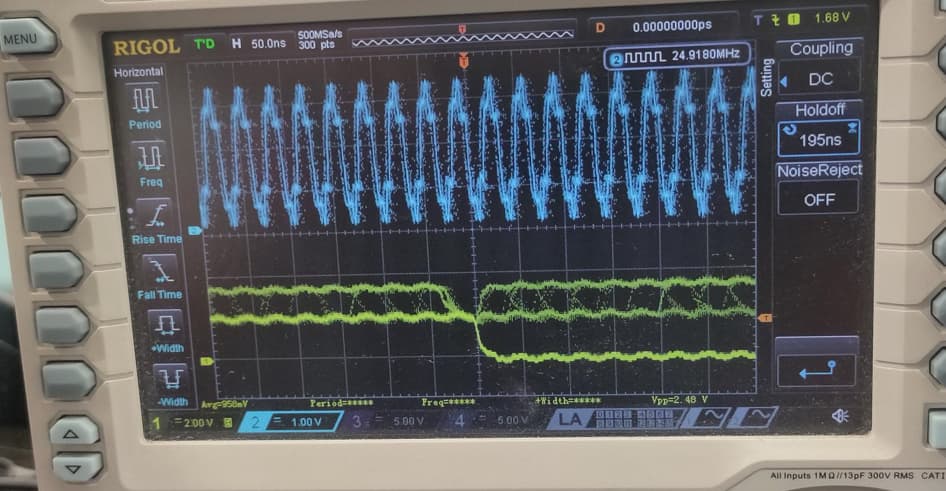

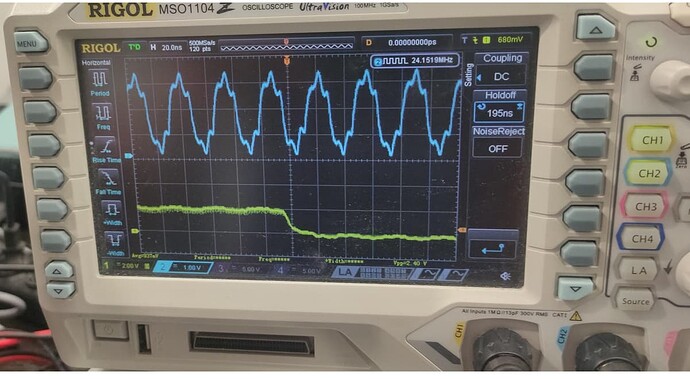

The problem that we have is that some pixels fliker, so for example, white letters on a black background produce noise and there is a cloud of white pixels filering around the letters.

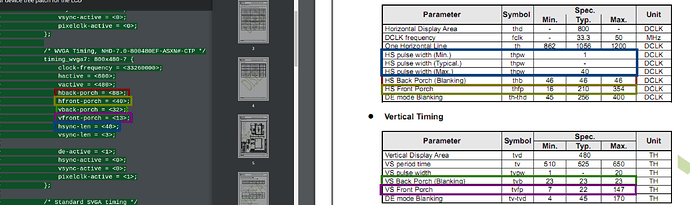

Our device tree patch for the LCD

imx7-colibri-viola.dtsi

+&lcdif {

+ display = <&display0>;

+ status = "okay";

+

+ display0: lcd-display {

+ bits-per-pixel = <16>;

+ bus-width = <18>;

+

+ display-timings {

+ native-mode = <&timing_wvga5>;

+

+ /* Standard VGA timing */

+ timing_vga: 640x480 {

+ clock-frequency = <25175000>;

+ hactive = <640>;

+ vactive = <480>;

+ hback-porch = <40>;

+ hfront-porch = <24>;

+ vback-porch = <32>;

+ vfront-porch = <11>;

+ hsync-len = <96>;

+ vsync-len = <2>;

+

+ de-active = <1>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ pixelclk-active = <0>;

+ };

+

+ /* WVGA Timing, PH800480T024-IBC01 */

+ timing_wvga5: 800x480-5 {

+ clock-frequency = <33300000>;

+ hactive = <800>;

+ hback-porch = <46>;

+ hfront-porch = <210>;

+ vactive = <480>;

+ vback-porch = <23>;

+ vfront-porch = <22>;

+ hsync-len = <20>;

+ vsync-len = <20>;

+

+ de-active = <1>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ pixelclk-active = <0>;

+ };

+

+ /* WVGA Timing, NHD-7.0-800480EF-ASXN#-CTP */

+ timing_wvga7: 800x480-7 {

+ clock-frequency = <33260000>;

+ hactive = <800>;

+ vactive = <480>;

+ hback-porch = <88>;

+ hfront-porch = <40>;

+ vback-porch = <32>;

+ vfront-porch = <13>;

+ hsync-len = <48>;

+ vsync-len = <3>;

+

+ de-active = <1>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ pixelclk-active = <1>;

+ };

+

+ /* Standard SVGA timing */

+ timing_svga: 800x600 {

+ clock-frequency = <40000000>;

+ hactive = <800>;

+ vactive = <600>;

+ hback-porch = <88>;

+ hfront-porch = <40>;

+ vback-porch = <23>;

+ vfront-porch = <1>;

+ hsync-len = <128>;

+ vsync-len = <4>;

+

+ de-active = <1>;

+ hsync-active = <1>;

+ vsync-active = <1>;

+ pixelclk-active = <0>;

+ };

+

+ /* Standard XGA timing */

+ timing_xga: 1024x768 {

+ clock-frequency = <65000000>;

+ hactive = <1024>;

+ vactive = <768>;

+ hback-porch = <160>;

+ hfront-porch = <24>;

+ vback-porch = <29>;

+ vfront-porch = <3>;

+ hsync-len = <136>;

+ vsync-len = <6>;

+

+ de-active = <1>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ pixelclk-active = <0>;

+ };

+ };

+ };

+};

Changes in the mxc_lcdif.c driver:

drivers/video/fbdev/mxc/mxc_lcdif.c

@@ -37,6 +37,18 @@ struct mxc_lcdif_data {

static struct fb_videomode lcdif_modedb[] = {

{

+ /* 800x480 @ 60 Hz , pixel clk @ 33.26MHz */

+ "NHD-7", 60, 800, 480, 30066,

+ .left_margin = 88,

+ .right_margin = 40,

+ .hsync_len = 128,

+ .upper_margin = 32,

+ .lower_margin = 13,

+ .vsync_len = 45,

+ .sync = FB_SYNC_CLK_LAT_FALL,

+ .vmode = FB_VMODE_NONINTERLACED,

+ .flag = 0,},

+ {

Here a video with the problem (look at lettes “e” and “a”:

Here the datasheet:

ZW-T070SWH-40CP Spec-3.pdf (1.6 MB)

Regards.

Juan Carlos