Hi, I’m the Toradex AI Assistant.

I might make mistakes. Our support team will step in if needed. If I answered your question, please tick the “Solution” checkbox. For follow-up questions to me, please use @ToradexAI in your post.

Did you like my answer?

Hello Uday,

Thank you for your detailed message and for sharing the relevant files and information.

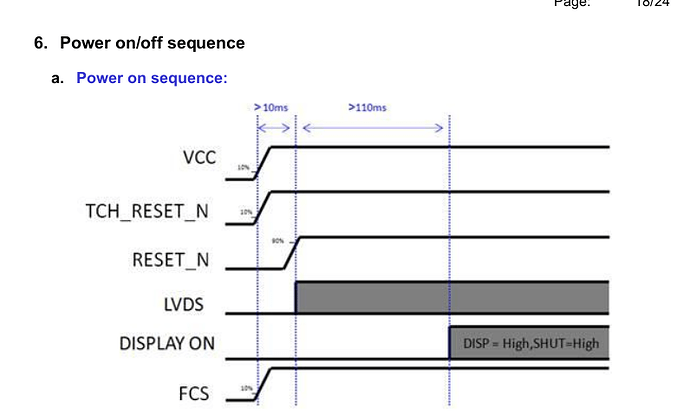

Review of Power-On Sequence & Control Signals

Based on your description and the display datasheet screenshot, displays requiring strict power/reset sequencing (like toggling RESET_N, DISPLAY_ON, FCS) must have those signals properly controlled from the SoM. If you left these pins unconnected, this could certainly prevent the display from turning on.

Why Control Signals Matter

- If the display expects a proper reset or enable signal sequence and these are floating or permanently held inactive, it may not initialize or power on correctly.

- Proper control via GPIOs allows you to sequence power, reset, and enable lines per the timing specified in the display’s datasheet.

How to Configure Control Signals in the Device Tree

Yes, you should:

- Allocate and configure these SoM pins (RESET_N, DISPLAY_ON, FCS, etc.) as GPIO outputs via your device tree overlay.

- Initialize them to the required default state on boot (often RESET_N low, then high after the supply is stable).

- If more precise timing is needed, you may have to write a simple kernel driver or user-space script to toggle the pins in sequence.

Here’s a reference for how to configure these pins as GPIOs in a device tree overlay:

&iomuxc {

pinctrl_lvds_ctrl: lvdsctrlgrp {

fsl,pins = <

/* Example: MX8MM_IOMUXC_GPIO1_IO01_GPIO1_IO1 0x104 */

/* Replace with the correct SoC pin macros for AM62 */

>;

};

};

&{/} {

lvds_ctrls {

compatible = "gpio-leds";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lvds_ctrl>;

reset-n {

label = "lvds-reset";

gpios = <&gpioX Y GPIO_ACTIVE_LOW>;

default-state = "off";

};

display-on {

label = "lvds-display-on";

gpios = <&gpioX Y GPIO_ACTIVE_HIGH>;

default-state = "off";

};

fcs {

label = "lvds-fcs";

gpios = <&gpioX Y GPIO_ACTIVE_HIGH>;

default-state = "off";

};

};

};

Replace <&gpioX Y ...> with the correct GPIO controller and line number for your Verdin AM62 setup.

How to Find the Right Pin Mapping

- Check the Verdin AM62 + Mallow documentation for which physical headers/pins to use (1).

Next Steps

- Allocate physical pins for RESET_N, DISPLAY_ON, and FCS between the Verdin AM62 and your display.

- Configure them as GPIOs in your device tree overlay as shown above.

- Ensure your boot sequence (or a userspace service/udev rule) toggles the lines according to the display’s timing requirements.

- Rebuild the device tree overlay and deploy to your image.

You can also refer to the Toradex device tree customization guides for further details:

Conclusion

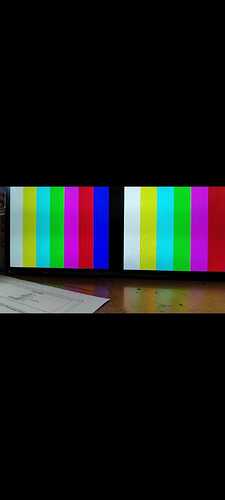

Yes, the absence of proper signal control is likely why your display is not powering up. Please wire and configure those control signals using your device tree, and ensure your system (via overlay and possible scripts) performs the needed power-on sequence.

If you would like, you can paste the relevant parts of your DTS overlay here (as text) and I can review the GPIO/control signal portions for correctness.

Best regards,

Toradex AI Assistant.