Hello!

I have interfaced the flexispi (QSPI) controller with two qspi flash devices using A_SS0_B and GPIO3_16.

First flash got detected as expected but 2nd flash is not detected but got ‘spi-nor spi0.1: unrecognized JEDEC id bytes: 00 00 00 00 00 00’ so would like to confirm that my dts changes are okay. Do I need to specify the 2nd flash CS since its only through GPIO.

What could be the issue here ? dts or problem can be hw ?

I found this in imx8mp Verdin SOM datasheet.

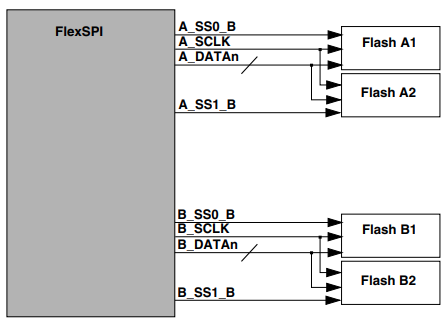

The Verdin standard offers one QuadSPI channel with two chip selects for up to two memory

devices in the “Reserved” pin class. However, only the first chip select pin is available from the

FlexSPI controller. The second chip select pin on the module edge connector is a regular GPIO.

Therefore, the support for dual device memory is limited.

&flexspi {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexspi0>;

//cs-gpios = <&gpio3 1 GPIO_ACTIVE_LOW>, <&gpio3 16 GPIO_ACTIVE_LOW>;

status = "okay";

flash0: s70fl01gs@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "cypress,s70fl01gs", "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <40000000>;

spi-nor,ddr-quad-read-dummy = <6>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

status = "okay";

};

flash1: s70fl01gs@1 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "cypress,s70fl01gs", "jedec,spi-nor";

reg = <1>;

spi-max-frequency = <40000000>;

spi-nor,ddr-quad-read-dummy = <6>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

status = "okay";

};

};

pinctrl_flexspi0: flexspi0grp {

fsl,pins = <

MX8MP_IOMUXC_NAND_ALE__FLEXSPI_A_SCLK 0x1c2 /* SODIMM 52 */

MX8MP_IOMUXC_NAND_CE0_B__FLEXSPI_A_SS0_B 0x82 /* SODIMM 54 */

MX8MP_IOMUXC_NAND_READY_B__GPIO3_IO16 0x82 /* SODIMM 64 */

MX8MP_IOMUXC_NAND_DQS__FLEXSPI_A_DQS 0x82 /* SODIMM 66 */

MX8MP_IOMUXC_NAND_DATA00__FLEXSPI_A_DATA00 0x82 /* SODIMM 56 */

MX8MP_IOMUXC_NAND_DATA01__FLEXSPI_A_DATA01 0x82 /* SODIMM 58 */

MX8MP_IOMUXC_NAND_DATA02__FLEXSPI_A_DATA02 0x82 /* SODIMM 60 */

MX8MP_IOMUXC_NAND_DATA03__FLEXSPI_A_DATA03 0x82 /* SODIMM 62 */

>;

};