Symptoms

● Occasionally see rx packets dropping on ttyLP0

● Bytes in the middle of the packet are dropped

● Communication recovers by itself for the next packet

● No pattern for reproducibility identified

Hardware Setup

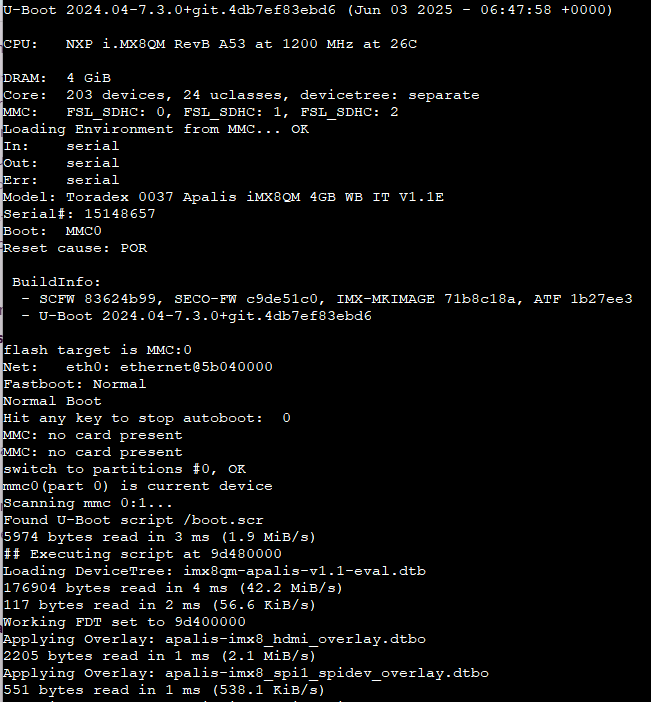

● Ixora Carrier board - v1.3A

● Apalis imx8qm

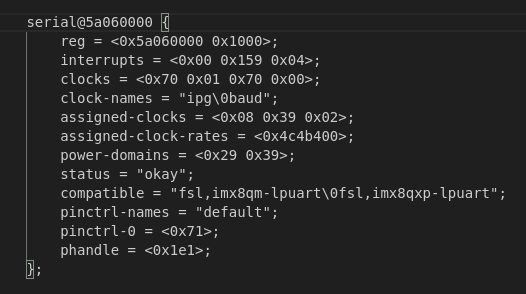

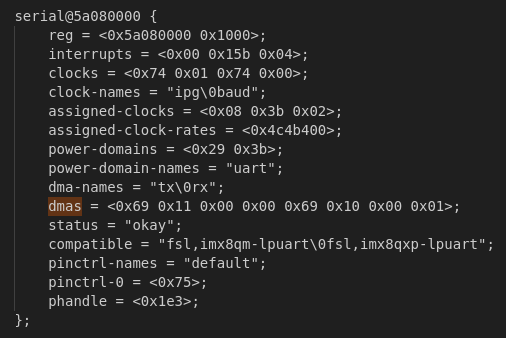

● UART peripherals in use - default device tree config:

○ ttyLP0 - UART 3 (according to datasheet), “No” DMA enabled

○ ttyLP2 - UART 4 (according to datasheet), edma2 enabled

○ No CTS/RTS being used or configured

● Snapshots of dts file obtained from live setup attached

Software Setup

● Baud - 921600

● On ttyLP0, the application process is run that receives a large

chunk of data ~8000 bytes every 2.5s-3s

● SW is configured with a batched size of 100 bytes in a single

UART transfer

RCH/Solutions tried

● Tried running the application code on ttyLP2 and don’t see any

errors indicating DMA may be required

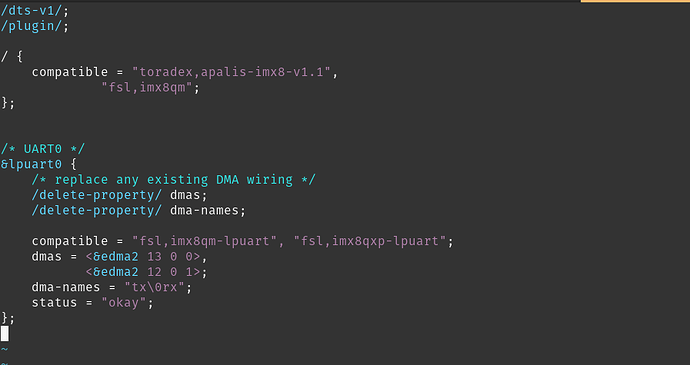

● Tried enabling DMA on ttyLP0 using overlays, but that doesn’t seem to show up in the system

● Below is the overlay that was attempted (used edma 2, ch 12/13 as that’s the default I saw after researching online)

Another observation is I see dma controller err on that channel (among others), not sure what that’s related to

Help Required

● If DMA needs to be enabled to resolve the issue (likely is), it would help to get feedback on the overlay and what am I doing wrong

● Is it advisable to compile the overlay on a system that doesn’t

have access to the full kernel source/without the torizon

builder

● If torizon builder needs to be used

○ Is it advisable to use an overlay?

○ Can the full device tree (with DMA enabled) be built instead of an overlay?

● Is there a specific reason DMA is disabled by default on ttyLP0

and if turning it ON may have any other side effects?