Hello all.

Please we need assitance from Technical Support.

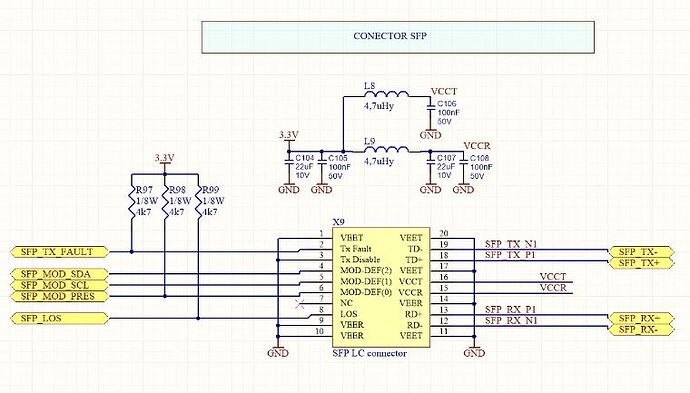

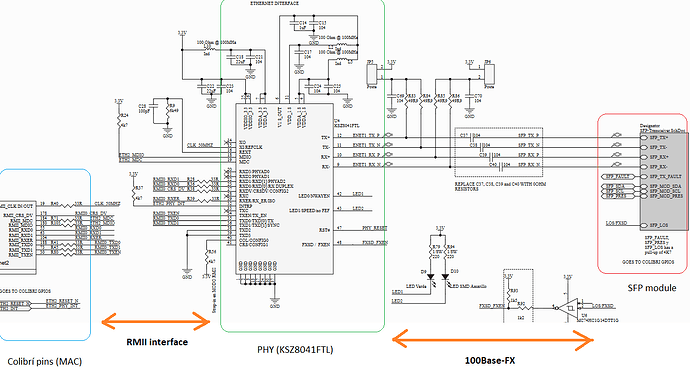

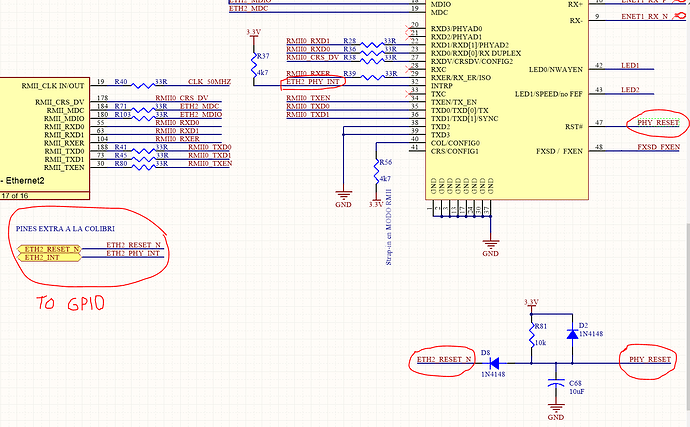

We have a Colibri module (imx6ULL) mounted in a custom carrier board and we want to use the 2nd ethernet interface (eth1) as an optical fiber link. The colibri is connected with an external PHY (in our case, we use the KSZ8041FTL capable of managing up to 100Base-FX) with RMII and MDIO protocols. Then, the PHY goes against an SFP optical transceiver module (in our case, we use the Fiberxon FTM-3401C-SL2G).

Our set up involves the first ethernet interface connected to a switch through an RJ-45 (that is working fine). Then, the second interface has a fibre patch connected to the transceiver, which then connects to a media converter which is connected to the same switch as the first interface.

Info about our SO and image

U-Boot 2020.07-5.7.0-devel+git.1cbeecee44a8 (Jun 27 2022 - 13:27:02 +0000)

CPU: Freescale i.MX6ULL rev1.1 900 MHz (running at 396 MHz)

----------------------------------------------------------------------

TDX X11 5.7.2-devel-20230830152423+build.0 (dunfell) colibri-imx6ull-06487386 ttymxc0

Colibri-iMX6ULL_Reference-Minimal-Image-x11

Our current status is that we managed to have the 2nd ethernet interface detected in Linux (driver assigned upon system start):

DMESG

root@colibri-imx6ull-06487386:~# dmesg | grep eth

[ 0.175406] eth_phy: supplied by +V3.3

[ 1.502299] fec 20b4000.ethernet eth0: registered PHC device 0

[ 2.515431] fec 2188000.ethernet eth1: registered PHC device 1

[ 18.212351] Micrel KSZ8041 20b4000.ethernet-1:02: attached PHY driver [Micrel KSZ8041] (mii_bus:phy_addr=20b4000.ethernet-1:02, irq=POLL)

[ 18.257811] Micrel KSZ8041 20b4000.ethernet-1:01: attached PHY driver [Micrel KSZ8041] (mii_bus:phy_addr=20b4000.ethernet-1:01, irq=POLL)

[ 20.330468] fec 20b4000.ethernet eth0: Link is Up - 100Mbps/Full - flow control rx/tx

[ 20.338624] IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

IFCONFIG

root@colibri-imx6ull-06487386:~# ifconfig

eth0 Link encap:Ethernet HWaddr 00:14:2D:62:FD:5A

inet addr:192.168.1.66 Bcast:192.168.1.255 Mask:255.255.255.0

inet6 addr: fe80::214:2dff:fe62:fd5a/64 Scope:Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:39572 errors:0 dropped:3 overruns:0 frame:0

TX packets:846 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:3112832 (2.9 MiB) TX bytes:193140 (188.6 KiB)

eth1 Link encap:Ethernet HWaddr 00:14:2D:72:FD:5A

UP BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

inet6 addr: ::1/128 Scope:Host

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:12 errors:0 dropped:0 overruns:0 frame:0

TX packets:12 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:1187 (1.1 KiB) TX bytes:1187 (1.1 KiB)

ip link show

root@colibri-imx6ull-06487386:~# ip link show

1: lo: <LOOPBACK,UP,LOWER_UP> mtu 65536 qdisc noqueue state UNKNOWN mode DEFAULT group default qlen 1000

link/loopback 00:00:00:00:00:00 brd 00:00:00:00:00:00

2: eth0: <BROADCAST,MULTICAST,DYNAMIC,UP,LOWER_UP> mtu 1500 qdisc pfifo_fast state UP mode DEFAULT group default qlen 1000

link/ether 00:14:2d:62:fd:5a brd ff:ff:ff:ff:ff:ff

3: eth1: <NO-CARRIER,BROADCAST,MULTICAST,DYNAMIC,UP> mtu 1500 qdisc pfifo_fast state DOWN mode DEFAULT group default qlen 1000

link/ether 00:14:2d:72:fd:5a brd ff:ff:ff:ff:ff:ff

networkctl -a

root@colibri-imx6ull-06487386:~# networkctl -a

IDX LINK TYPE OPERATIONAL SETUP

1 lo loopback carrier unmanaged

2 eth0 ether routable unmanaged

3 eth1 ether no-carrier unmanaged

3 links listed.

and with ethtool we can see that the PHY configuration seems correct:

[ethtool eth1]:

root@colibri-imx6ull-06487386:~# ethtool eth1

Settings for eth1:

Supported ports: [ FIBRE ]

Supported link modes: 100baseT/Half 100baseT/Full

Supported pause frame use: No

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: 100baseT/Half 100baseT/Full

Advertised pause frame use: No

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 100Mb/s

Duplex: Full

Port: MII

PHYAD: 1

Transceiver: internal

Auto-negotiation: off

Supports Wake-on: g

Wake-on: d

Link detected: no

Now, regarding the SFP module, we can only read its EEPROM, which has information about the transceiver itself (brand, serial number, model, etc) but that’s it, we are stuck there.

Searching through the internet, we found that linux has a layer called “phylink” that seems to handle this SFP modules dinamically, and we followed some examples in /Documentation/device tree/bindings/net/sff,sfp.txt.

But we are still in the same status. Here in the forum there isn´t much information regarding SFP modules, or even using colibri modules with fiber optics.

Our device tree looks like this:

DEVICE TREE

imx6ull-colibri.dtsi

/ {

...

sfp_eth0: sfp-eth0 {

compatible = "sff,sfp";

i2c-bus = <&i2c3>; // this is the bus where the transceiver's eeprom is mapped to

mod-def0-gpios = <&gpio3 22 GPIO_ACTIVE_LOW>; //MOD-DEF 0 is grounded by the module to indicate that the module is present

tx-fault-gpios = <&gpio3 21 GPIO_ACTIVE_HIGH>; //Logic 0 indicates normal operation; logic 1 indicates a laser fault of some kind.

};

}

--------------------------------------------------

&fec2 {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_enet2>;

pinctrl-1 = <&pinctrl_enet2_sleep>;

phy-mode = "rmii";

phy-handle = <ðphy2>;

phy-supply = <®_eth_phy>;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy2: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

max-speed = <100>;

reg = <2>;

fsl,mii-bus-wait-delay = <16>; /* 16 usec */

};

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

micrel,led-mode = <0>;

micrel,fiber-mode;

sfp = <&sfp_eth0>; // sacado de https://bootlin.com/blog/sfp-modules-on-a-board-running-linux/

reg = <1>;

max-speed = <100>;

fsl,mii-bus-wait-delay = <16>; /* 16 usec */

};

};

};

imx6ull-colibri-eval-v3.dtsi

...

&fec1 {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_enet1>;

pinctrl-1 = <&pinctrl_enet1_sleep>;

phy-mode = "rmii";

phy-reset-gpios = <&gpio3 2 GPIO_ACTIVE_LOW>;

interrupt-parent = <&gpio3>;

interrupts = <10 IRQ_TYPE_LEVEL_HIGH>;

phy-handle = <ðphy1>;

phy-supply = <®_eth_phy>;

status = "okay";

};

------------------------------------

...

&i2c3 {

status = "okay";

pinctrl-names = "default", "gpio";

pinctrl-0 = <&pinctrl_i2c3>;

pinctrl-1 = <&pinctrl_i2c3_gpio>;

sda-gpios = <&gpio3 5 (GPIO_ACTIVE_HIGH | GPIO_OPEN_DRAIN)>; // SODIMM 76

scl-gpios = <&gpio3 6 (GPIO_ACTIVE_HIGH | GPIO_OPEN_DRAIN)>; // SODIMM 70

eepromphy: at24c01a@50 {

compatible = "atmel,24c01";

pagesize = <8>;

reg = <0x50>;

};

};

- Is our device tree coherent or has something wrong?

- Are there any examples of how we should set the device tree in order to see the SFP module?

- How does the SFP module tells the PHY or the CPU that the link is UP or DOWN? Who controls that?

I attached the schematics of the Colibri-to-PHY, and the PHY-to-SFP transceiver.

Colibri-PHY.pdf (210.4 KB)

We want to know at least where to look for answers, if it might be hardware/pcb_routing or software because we are a bit lost here.

Hope a soon response.

Best regards,

Martin