Looking at our some of our device trees, we can see that the 12288Mhz clock is listed as an option to be used for our codecs:

sgtl5000: codec@a {

compatible = "fsl,sgtl5000";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sgtl5000>;

#sound-dai-cells = <0>;

assigned-clocks = <&clk IMX_SC_R_AUDIO_PLL_0 IMX_SC_PM_CLK_PLL>,

<&clk IMX_SC_R_AUDIO_PLL_0 IMX_SC_PM_CLK_SLV_BUS>,

<&clk IMX_SC_R_AUDIO_PLL_0 IMX_SC_PM_CLK_MST_BUS>,

<&mclkout0_lpcg 0>;

assigned-clock-rates = <786432000>, <49152000>, <12288000>, <12288000>;

clocks = <&mclkout0_lpcg 0>;

clock-names = "mclk";

reg = <0x0a>;

VDDA-supply = <®_module_3v3_avdd>;

VDDD-supply = <®_vref_1v8>;

VDDIO-supply = <®_module_3v3>;

};

http://git.toradex.cn/cgit/linux-toradex.git/tree/arch/arm64/boot/dts/freescale/imx8-apalis-v1.1.dtsi?h=toradex_5.4-2.3.x-imx#n369

Because of this I would say that if the customer wants to keep using the same clock, it should be possible. Other possible clocks are listed there as well.

If the codec is not configured in standalone mode (i.e. it has the I2C lines connected), it can be controlled by software. Here’s the clock initialization function from the codec driver in the linux kernel:

/**

* cs4270_set_dai_sysclk - determine the CS4270 samples rates.

* @codec_dai: the codec DAI

* @clk_id: the clock ID (ignored)

* @freq: the MCLK input frequency

* @dir: the clock direction (ignored)

*

* This function is used to tell the codec driver what the input MCLK

* frequency is.

*

* The value of MCLK is used to determine which sample rates are supported

* by the CS4270. The ratio of MCLK / Fs must be equal to one of nine

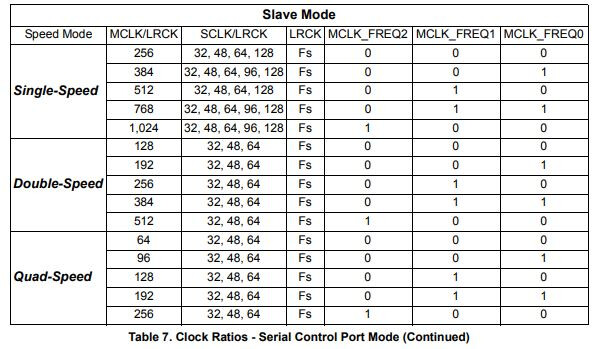

* supported values - 64, 96, 128, 192, 256, 384, 512, 768, and 1024.

*

* This function calculates the nine ratios and determines which ones match

* a standard sample rate. If there's a match, then it is added to the list

* of supported sample rates.

*

http://git.toradex.cn/cgit/linux-toradex.git/tree/sound/soc/codecs/cs4270.c?h=toradex_5.4-2.3.x-imx#n228

This gives a good idea of what clock rates should be supported by the codec, and it reflects the table given in the question.

Best regards,

Rafael Beims