Hello,

I’m working on a custom carrier board housing a Colibri iMX8DX 1GB WB module. The end goal is to get an analog camera working using the ADV7280 through the parallel CSI interface (not MIPI CSI-2).

I couldn’t find an example for that particular usage (iMX8X + ADV7280).

Those are the relevant parts of the device tree:

&i2c1 {

clock-frequency = <100000>;

status = "okay";

adv_7280: adv7280@20 {

compatible = "adi,adv7280";

reg = <0x20>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_parallel_csi>;

reset-gpios = <&lsio_gpio3 12 GPIO_ACTIVE_LOW>; // SODIMM_71

powerdown-gpios = <&lsio_gpio3 21 GPIO_ACTIVE_LOW>; // SODIMM_98

// csi_id = <0>;

mclk = <27000000>;

status = "okay";

port {

adv7280_ep: endpoint@3 {

reg = <3>; // AIN4

remote-endpoint = <¶llel_csi_ep>; // Link to parallel csi endpoint

bus-type = <5>; // Parallel

bus-width = <8>; // 8-bit

data-shift = <2>; // D2-D9 are used

vsync-active = <1>;

hsync-active = <1>;

pclk-sample = <1>;

};

};

};

};

&mipi_csi_0 {

status = "disabled";

};

&cameradev {

parallel_csi;

status = "okay";

};

&isi_1 {

interface = <6 0 2>;

status = "okay";

cap_device {

status = "okay";

};

};

¶llel_csi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

port@0 {

reg = <0>;

parallel_csi_ep: endpoint {

remote-endpoint = <&adv7280_ep>; // Link to adv7280 endpoint

};

};

};

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_newhog0>, <&pinctrl_hog1>,

<&pinctrl_lcd>, <&pinctrl_keepalive>;

pinctrl_keepalive: keepalive_pingrp {

fsl,pins =

<IMX8QXP_SPDIF0_EXT_CLK_LSIO_GPIO0_IO12 0x46000061>; /* Keep_alive: output */

};

pinctrl_lcd: lcd_pingrp {

fsl,pins =

<IMX8QXP_ESAI0_FSR_ADMA_LCDIF_D00 0x00000060>, /* LCD_BL: input */

<IMX8QXP_USDHC1_WP_LSIO_GPIO4_IO21 0x46000061>; /* LCD_BL: output */

};

pinctrl_newhog0: newhog0grp {

fsl,pins =

<IMX8QXP_QSPI0A_DATA2_LSIO_GPIO3_IO11 0x20>, /* SODIMM 69 */

<IMX8QXP_SAI0_TXC_LSIO_GPIO0_IO26 0x20>, /* SODIMM 79 */

<IMX8QXP_ENET0_RGMII_RXC_LSIO_GPIO5_IO03 0x06000020>, /* SODIMM 85 */

<IMX8QXP_QSPI0B_SCLK_LSIO_GPIO3_IO17 0x20>, /* SODIMM 95 */

<IMX8QXP_SAI0_RXD_LSIO_GPIO0_IO27 0x20>, /* SODIMM 97 */

<IMX8QXP_QSPI0B_DATA0_LSIO_GPIO3_IO18 0x20>, /* SODIMM 99 */

<IMX8QXP_SAI0_TXFS_LSIO_GPIO0_IO28 0x20>, /* SODIMM 101 */

<IMX8QXP_SAI0_TXD_LSIO_GPIO0_IO25 0x20>, /* SODIMM 103 */

<IMX8QXP_QSPI0B_DATA1_LSIO_GPIO3_IO19 0x20>, /* SODIMM 105 */

<IMX8QXP_USB_SS3_TC2_LSIO_GPIO4_IO05 0x20>, /* SODIMM 127 */

<IMX8QXP_USB_SS3_TC3_LSIO_GPIO4_IO06 0x20>, /* SODIMM 131 */

<IMX8QXP_USB_SS3_TC1_LSIO_GPIO4_IO04 0x20>, /* SODIMM 133 */

<IMX8QXP_SAI1_RXFS_LSIO_GPIO0_IO31 0x20>, /* SODIMM 100 */

<IMX8QXP_QSPI0B_DQS_LSIO_GPIO3_IO22 0x20>, /* SODIMM 102 */

<IMX8QXP_QSPI0B_SS0_B_LSIO_GPIO3_IO23 0x20>; /* SODIMM 104 */

};

// ADV7280 parallel video interface

pinctrl_parallel_csi: parallelcsigrp {

fsl,pins =

<IMX8QXP_CSI_D00_CI_PI_D02 0xC0000041>,

<IMX8QXP_CSI_D01_CI_PI_D03 0xC0000041>,

<IMX8QXP_CSI_D02_CI_PI_D04 0xC0000041>,

<IMX8QXP_CSI_D03_CI_PI_D05 0xC0000041>,

<IMX8QXP_CSI_D04_CI_PI_D06 0xC0000041>,

<IMX8QXP_CSI_D05_CI_PI_D07 0xC0000041>,

<IMX8QXP_CSI_D06_CI_PI_D08 0xC0000041>,

<IMX8QXP_CSI_D07_CI_PI_D09 0xC0000041>,

<IMX8QXP_CSI_PCLK_CI_PI_PCLK 0xC0000041>,

<IMX8QXP_CSI_HSYNC_CI_PI_HSYNC 0xC0000041>,

<IMX8QXP_CSI_VSYNC_CI_PI_VSYNC 0xC0000041>,

<IMX8QXP_CSI_MCLK_CI_PI_MCLK 0xC0000041>,

<IMX8QXP_QSPI0A_DATA3_LSIO_GPIO3_IO12 0xC6000041>, // SODIMM 98

<IMX8QXP_QSPI0B_DATA3_LSIO_GPIO3_IO21 0xC6000041>; // SODIMM 71

};

};

pinctrl_hog2 was removed from pinctrl-0 in iomuxc because SODIMM_75 was in conflict.

Here’s what I’ve got so far:

- I compiled the ADV7180 driver. It’s loaded and it found the chip via i2c.

dmesg | grep adv7gives

adv7180 1-0020: chip id 0x43 found @ 0x20 (5a810000.i2c) - Something related to the image sensor interface is also working, but then there’s a problem:

[ 1.463013] mxc-isi 58110000.isi: mxc_isi.1 registered successfully

[ 1.569492] mxc-parallel-csi 58261000.pcsi: mxc_parallel_csi_probe probe successfully

[ 10.507140] imx8_media_dev: module is from the staging directory, the quality is unknown, you have been warned.

[ 10.540520] mx8-img-md: Registered mxc_isi.1.capture as /dev/video2

[ 10.570707] unregister ISI channel: mxc_isi.1

[ 10.826565] mxc-jpeg 58400000.jpegdec: decoder device registered as /dev/video2 (81,2)

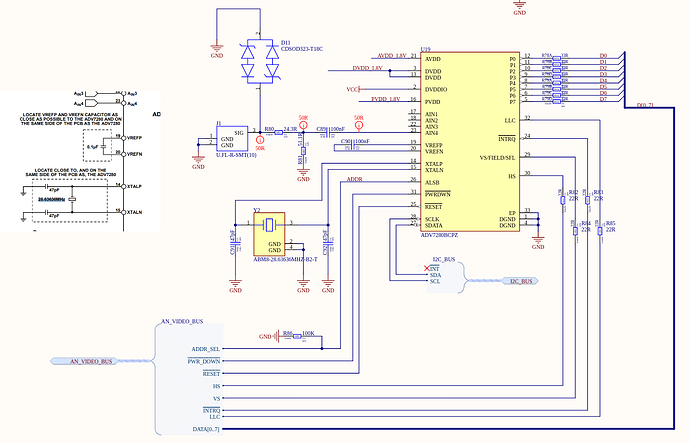

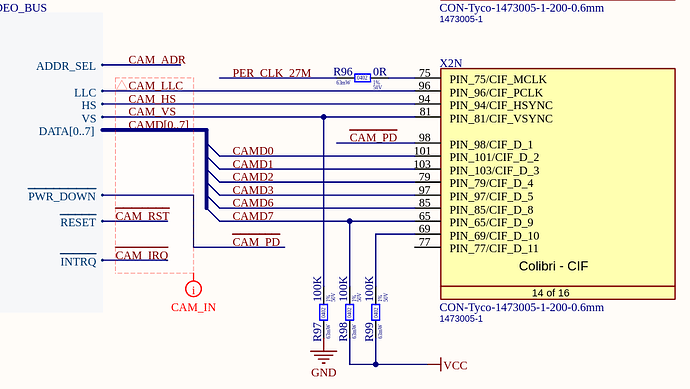

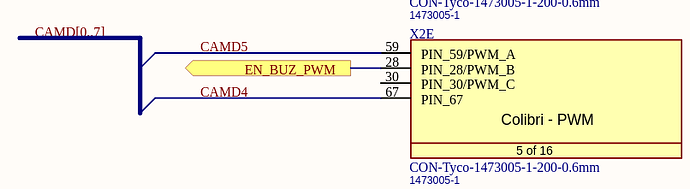

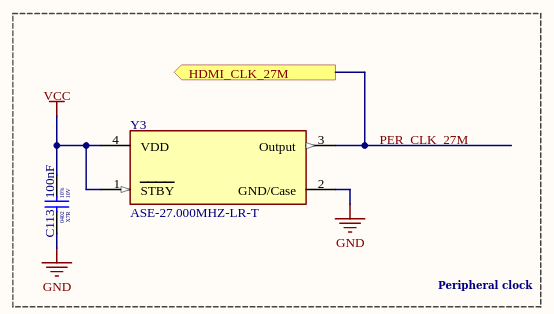

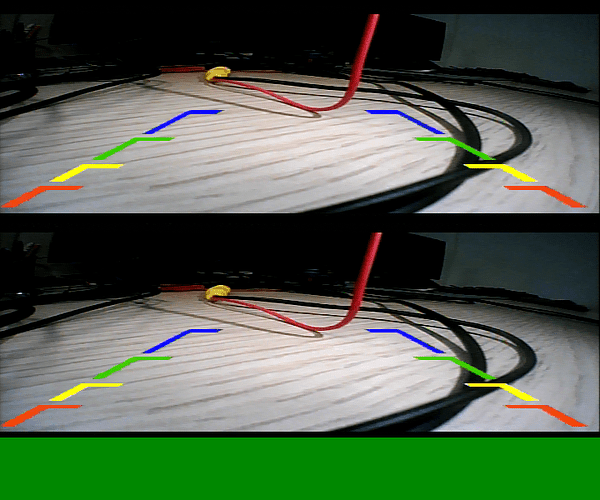

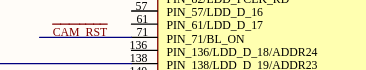

Here are are the relevant parts of the schematic:

ADV7280 side:

SoM side:

As far as I understand, the video device gets created but it is later overwritten by mxc-jpeg.

I assume there’s something missing or misconfigured in the device tree.

What can I do to get the video device working?

Thank you in advance for any help provided.

Hardware info:

Custom board

SoM: Colibri iMX8DX 1GB WB

OS: Custom based on torizon-core-docker-colibri-imx8x-Tezi_6.3.0+build.4

Kernel version: Linux 5.15.77-6.3.0+git.ddc6ca4d76ea

Full dmesg log: dmesg.txt (30.0 KB)