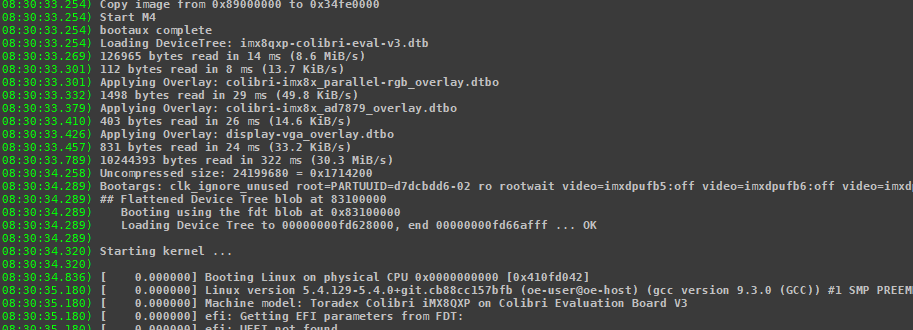

Before start my questions, device tree sources for “imx8qxp-colibri-eval-v3.dtb” are fundamentally these:

Please, correct me if I’m wrong.

clk_summary info.txt (33.7 KB)

I’ve attached the information given by clk_summary.

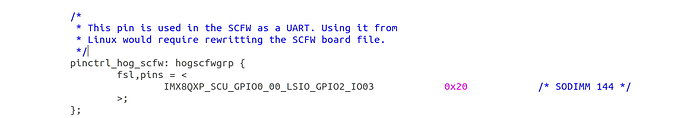

There is only this mentions to CM4.

enable prepare protect duty

clock count count count rate accuracy phase cycle

---------------------------------------------------------------------------------------------

cm40_i2c_div 0 0 0 0 0 0 50000

cm40_lpcg_i2c_clk 0 0 0 0 0 0 50000

cm40_ipg_clk 0 0 0 132000000 0 0 50000

cm40_lpcg_i2c_ipg_clk 0 0 0 132000000 0 0 50000

¿Is there any mention in device tree sources about this? I can find it.

I tried to understand how are configured the ADMA UARTS also.

For example, we have this for UART0:

uart0_lpcg_ipg_clk 0 0 0 160000000 0 0 50000

uart0_clk 0 0 0 80000000 0 0 50000

uart0_lpcg_baud_clk 0 0 0 80000000 0 0 50000

The only I’ve found this…

“imx8x-colibri-eval-v3.dtsi”

&lpuart0 {

status = "okay";

};

“imx8x-colibri.dtsi”

&lpuart0 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lpuart0>;

};

pinctrl_lpuart0: lpuart0grp {

fsl,pins = <

IMX8QXP_UART0_RX_ADMA_UART0_RX 0x06000020 /* SODIMM 36 */

IMX8QXP_UART0_TX_ADMA_UART0_TX 0x06000020 /* SODIMM 38 */

IMX8QXP_FLEXCAN0_RX_ADMA_UART0_RTS_B 0x06000020 /* SODIMM 34 */

IMX8QXP_FLEXCAN0_TX_ADMA_UART0_CTS_B 0x06000020 /* SODIMM 32 */

>;

};

“imx8qxp.dtsi”

aliases {

serial0 = &lpuart0;

};

And this is it. Nothing else apparently.

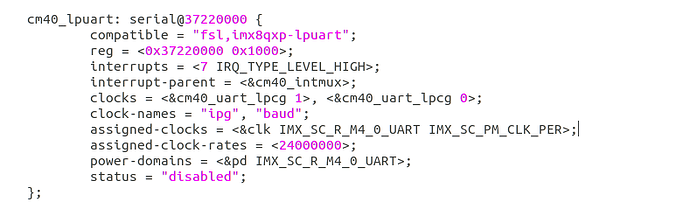

The only mention to the clock used by this uart, is in “imx8-ss-dma.dtsi”. As it was for CM4 UART in “imx8-ss-cm40.dtsi”

¿Why ADMA UART clocks are visible and why CM4 clock aren’t? I followed the same steps in order I could make CM4_UART clock working enabling this UART in linux only for understanding, but didn’t worked.

In file “imx8qxp.dtsi” there is a mention to which seems to be the primary clock sources.

clk: clock-controller {

compatible = "fsl,imx8qxp-clk", "fsl,scu-clk";

#clock-cells = <2>;

clocks = <&xtal32k &xtal24m>;

clock-names = "xtal_32KHz", "xtal_24Mhz";

};

I can’t follow more clues about clock sources are activated in device tree structure. Because of this, come to my mind more questions.

¿Are you sure that the issue lies in device tree configuration? I maintain some suspects about hardware partitioning made by SCU

¿Are you aware if someone has used M4UART with Colibri IMX8 before?

I really beg you to reproduce this issue from your side. I’m pretty sure that you can determine more quickly what is happenning.

I am running out of time and it is essential that I be able to use all the available UARTs of the Colibri IMX8. There aren’t so much sense that this will be possible by hardware, since you have routed to SODIMM pins and then it won’t be able using Linux on A35 side.

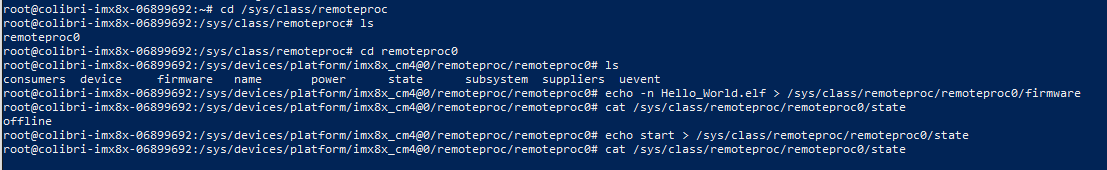

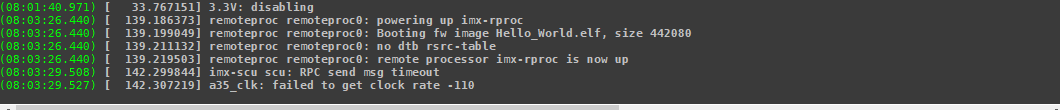

Thank you very much for the indications of how can be loaded M4 firmware from A35 side. I will investigate further about that topics. And if I can, I will try to run M4 firmware like that to check if M4_UART works. But please, take in consideration that is not a real solution to my main problem.

I look forward to more information, @Edward. Thank you.