Hello all to whom it may concern,

I am currently designing the USB3 connection application based on Apalis iMX8QM board and have got substantially good results of phy characteristics

except tx eye opening, which is slightly cross the limit…

As far as I understand, the host MPU of NXP/iMX8Q’s PCIe transceiver has some register to tune the voltage swing for adopting some application purpose (such as eye opening), and USB3 PIPE I/F have similar PHY structure so that it may be possible

to access and set the appropriate value for satisfying USB3 requirement.

Reviewing iMX8 Reference manual, I could not find any related results for the setup register especially TxMargin[2…0],TxSwing.

I am also trying to improve the artwork of USB differencial pair much more precisely, however does someone who knows about that more details of register setting for USB3?

Or is there any solution to improve the voltage swing for USB3 signal lane?

I am looking forward to see your comments, thank you very much in advance.

Hi @KT_tsuchida , sorry for the delay.

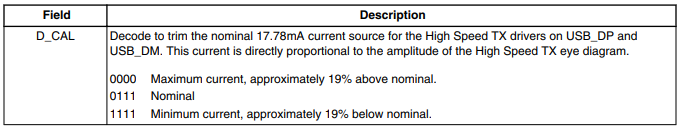

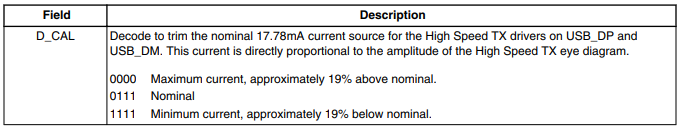

One preliminary answer but I know that we had USB 2.0 Compliance in Colibri iMX8X issues with default values. The register in question was D_CAL.

Since this was with the i.MX8X I’m not sure if the iMX8 has similar values, but after increasing the current (0000-0101) the module passed the compliance test.

I also found this application note from NXP: https://www.nxp.com/docs/en/application-note/AN12409.pdf

For your case, I would check 8.3 i.MX 8QXP/8QM USB PHY registers and software configurations

Kind regards,

Alvaro.

Hello Alvaro-san, thank you very much for your first kind reply.

I had read AN12409 for my study but I could not find exact answer for the USB3 register setup… would you please ask also NXP for more detail?

regards,

Tsuchida

This question was already asked to NXP and answered: Solved: Re: USB2/3 Compliance Testing in i.mx8QM - NXP Community

Checking the USB compliance documentation, there is no mention of such TxMargin. Instead the following registers are mentioned:

|

USB3_PHY3P0(5B16_0000) |

|

USB3 (5B12_0000) |

Why do you think these registers have relationship with the compliance process?

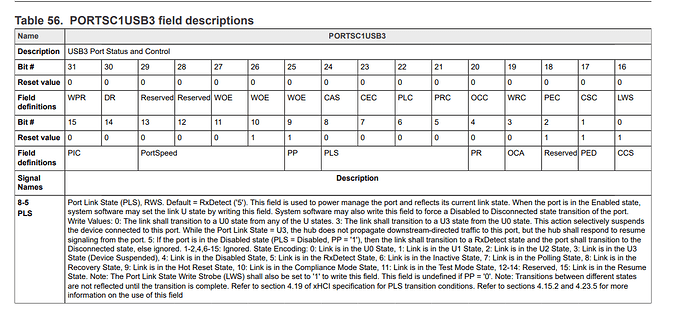

Have you tried adjusting the PORTSC1USB3?

8.3.4.5 Adjust USB3.0 to compliance mode registers–PORTSC1USB3

0x5b130490=0x0a000340

8.4 i.MX 8M USB PHY Registers and Software Configurations

8.4.1 Operation steps

8.4.1.1 Type C port

8.4.1.1.1 USB3.0 Host mode

Kind regards,

Alvaro.