I currently am able to send and recieve data from Core M4_0, however am unable to send or recieve data from the Core M4_1. This is before i even set up the linux side. I have altered the Device tree to prevent linux taking control of the M4 uart’s, but require use of both core’s tighly coupled uart.

I have done the following:

on the eval board:

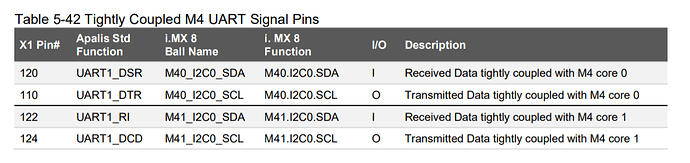

Removed:

- X6-40 (MXM3_110)

- X6-35 (MXM3_120)

- X6-34 (MXM3_122)

- X6-33 (MXM3_124)

Connected:

- X5-40 (MXM3_110) → TLL USB1 RX

- X5-35 (MXM3_120) → TLL USB1 TX

- X5-34 (MXM3_122) → TLL USB2 RX

- X5-35 (MXM3_124) → TLL USB2 TX

and in board.h

#if defined(MIMX8QM_CM4_CORE0)

#define BOARD_DEBUG_UART_BASEADDR (uint32_t) CM4_0__LPUART

#define BOARD_DEBUG_UART_INSTANCE 0U

#define BOARD_DEBUG_UART_SC_RSRC SC_R_M4_0_UART

#define BOARD_DEBUG_UART_CLKSRC kCLOCK_M4_0_Lpuart

#define BOARD_UART_IRQ M4_0_LPUART_IRQn

#define BOARD_UART_IRQ_HANDLER M4_0_LPUART_IRQHandler

#elif defined(MIMX8QM_CM4_CORE1)

#define BOARD_DEBUG_UART_BASEADDR (uint32_t) CM4_1__LPUART

#define BOARD_DEBUG_UART_INSTANCE 1U

#define BOARD_DEBUG_UART_SC_RSRC SC_R_M4_1_UART

#define BOARD_DEBUG_UART_CLKSRC kCLOCK_M4_1_Lpuart

#define BOARD_UART_IRQ M4_1_LPUART_IRQn

#define BOARD_UART_IRQ_HANDLER M4_1_LPUART_IRQHandler

#else

#error "No valid BOARD_DEBUG_UART_BASEADDR defined."

#endif

Is there a step i have missed to use the both tightly coupled uarts on the M4Cores ?

N.B.

i have tried using example code and am able to use DMA_Uart2, however we required use of tightly coupled uarts.

UPDATE:

i have updated this into the pin_mux.c

void BOARD_InitPins(sc_ipc_t ipc) /*!< Function assigned for the core: Cortex-M4F[cm4_core0] */

{

sc_err_t err = SC_ERR_NONE;

#if defined(MIMX8QM_CM4_CORE0)

err = sc_pad_set_all(ipc, SC_P_M40_I2C0_SCL, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SCL register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

err = sc_pad_set_all(ipc, SC_P_M40_I2C0_SCL, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SDA register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

#elif defined(MIMX8QM_CM4_CORE1)

err = sc_pad_set_all(ipc, SC_P_M41_I2C0_SCL, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SCL register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

err = sc_pad_set_all(ipc, SC_P_M41_I2C0_SCL, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SDA register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

#endif

}

found the solution:

board.h is correct. however pin_mux.c and pin_mux.h are incorrect.

here is the pinmux solution:

pin_mux.c

void BOARD_InitPins(sc_ipc_t ipc) /*!< Function assigned for the core: Cortex-M4F[cm4_core_X] */

{

sc_err_t err = SC_ERR_NONE;

//mux -> alt mode?

err = sc_pad_set_all(ipc, BOARD_INITPINS_RX, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SCL register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

err = sc_pad_set_all(ipc, BOARD_INITPINS_TX, 1U, SC_PAD_CONFIG_NORMAL, SC_PAD_ISO_OFF, 0x0 ,SC_PAD_WAKEUP_OFF);/* IOMUXD_M40_I2C0_SDA register modification value */

if (SC_ERR_NONE != err)

{

assert(false);

}

}

pin_mux.h

/*

* Copyright 2017-2020 NXP

*

* SPDX-License-Identifier: BSD-3-Clause

*/

#ifndef _PIN_MUX_H_

#define _PIN_MUX_H_

#include "board.h"

/***********************************************************************************************************************

* Definitions

**********************************************************************************************************************/

#if defined(MIMX8QM_CM4_CORE0)

#define BOARD_INITPINS_TX SC_P_M40_I2C0_SDA /*!< Pin function id */

#define BOARD_INITPINS_RX SC_P_M40_I2C0_SCL /*!< Pin function id */

#elif defined(MIMX8QM_CM4_CORE1)

#define BOARD_INITPINS_TX SC_P_M41_I2C0_SDA /*!< Pin function id */

#define BOARD_INITPINS_RX SC_P_M41_I2C0_SCL /*!< Pin function id */

#else

#error pin config not set

#endif

/*!

* @addtogroup pin_mux

* @{

*/

/***********************************************************************************************************************

* API

**********************************************************************************************************************/

#if defined(__cplusplus)

extern "C" {

#endif

/*!

* @brief Calls initialization functions.

*

*/

void BOARD_InitBootPins(void);

/*!

* @brief Configures pin routing and optionally pin electrical features.

* @param ipc scfw ipchandle.

*

*/

void BOARD_InitPins(sc_ipc_t ipc); /*!< Function assigned for the core: Cortex-M4F[cm4_core0] */

#if defined(__cplusplus)

}

#endif

/*!

* @}

*/

#endif /* _PIN_MUX_H_ */

/***********************************************************************************************************************

* EOF

**********************************************************************************************************************/