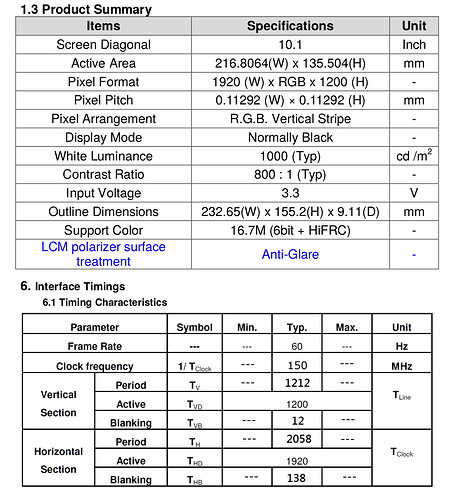

I have an Apalis IMX6q, on an Ixora carier and want to attach an LVDS display 1920x1200 that use 2 channels LVDS.

I configured DTS in this way:

diff --git a/arch/arm/boot/dts/imx6qdl-apalis.dtsi b/arch/arm/boot/dts/imx6qdl-apalis.dtsi

index cebd78f2a34e..78b8c3bc83c2 100644

--- a/arch/arm/boot/dts/imx6qdl-apalis.dtsi

+++ b/arch/arm/boot/dts/imx6qdl-apalis.dtsi

@@ -92,10 +92,10 @@

mxcfb1: fb@0 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "ldb";

- interface_pix_fmt = "RGB666";

- default_bpp = <16>;

+ interface_pix_fmt = "LVDS666";

+ default_bpp = <32>;

int_clk = <0>;

status = "disabled";

};

@@ -523,19 +523,34 @@

&ldb {

status = "okay";

-// split-mode;

+ split-mode;

// dual-mode;

lvds-channel@0 {

reg = <0>;

fsl,data-mapping = "spwg"; /* "jeida"; */

- fsl,data-width = <18>;

+ fsl,data-width = <24>;

crtc = "ipu2-di1";

primary;

status = "okay";

display-timings {

- native-mode = <&timing_xga>;

+ native-mode = <&timing_wuxga>;

+ timing_wuxga: 1920x1200M {

+ clock-frequency = <149992500>;

+ hactive = <1920>;

+ hback-porch = <20>;

+ hfront-porch = <100>;

+ hsync-len = <18>;

+ hsync-active = <0>;

+ vactive = <1200>;

+ vback-porch = <4>;

+ vfront-porch = <6>;

+ vsync-len = <2>;

+ vsync-active = <0>;

+ de-active = <1>;

+ pixelclk-active = <0>;

+ };

/* LDB-AM-800600LTNQW-A0H */

timing_svga: 800x600 {

clock-frequency = <55000000>;

And if I start the kernel with:

setenv vidargs 'video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M'

I get bad image:

[upload|gfL8fa19pZxIDsb0JXA85eE+JV8=]

But the time parameters are configured correctly:

[ 24.102946] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

root@apalis-imx6:~# [ 24.301451] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

[ 24.399321] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

[ 24.499760] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

root@apalis-imx6:~# [ 31.827127] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

root@apalis-imx6:~#

root@apalis-imx6:~# [ 36.313123] usb_otg_vbus: disabling

fbset

mode "1920x1200-60"

# D: 149.993 MHz, H: 72.883 kHz, V: 60.134 Hz

geometry 1920 1200 1920 1200 32

timings 6667 20 100 4 6 18 2

rgba 8/16,8/8,8/0,8/24

endmode

Noting that the right side seems stretched, like the secondary channel is not configured or configured with a bad parameters

Now if I start the kernel with this parameters

setenv vidargs 'video=mxcfb0:dev=ldb,1920x1200M@60,if=LVDS666 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M'

It will seems better (there are some flickerig and bad timing parameters configured, the clock is very high 194Mhz (why?!?!))

[upload|+MDKBXGOiep+Lns86XOP9qaMNsU=]

[ 13.098593] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 200,136,336 v_sync,l,u: 6,3,36 pixclock=193274000 Hz

[ 13.289203] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 200,136,336 v_sync,l,u: 6,3,36 pixclock=193274000 Hz

[ 13.366268] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 200,136,336 v_sync,l,u: 6,3,36 pixclock=193274000 Hz

[ 13.436650] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 200,136,336 v_sync,l,u: 6,3,36 pixclock=193274000 Hz

[ 13.448381] IPv6: ADDRCONF(NETDEV_UP): usb0: link is not ready

[ 14.042231] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 200,lock=193274000 Hz

[ 36.313195] usb_otg_vbus: disabling

root@apalis-imx6:~#

root@apalis-imx6:~#

root@apalis-imx6:~# fbset

mode "1920x1200-60"

# D: 193.274 MHz, H: 74.566 kHz, V: 59.892 Hz

geometry 1920 1200 1920 1200 32

timings 5174 336 136 36 3 200 6

vsync high

rgba 8/16,8/8,8/0,8/24

The parameters are not what I configured in DTS, and if I set them with fbset

root@apalis-imx6:~# fbset -t 6667 20 100 4 6 18 2 -vsync false -g 1920 1200 1920 1200 32 -s

[ 225.206666] mxc_sdc_fb fb@0: 1920x1200 h_sync,r,l: 18,100,20 v_sync,l,u: 2,6,4 pixclock=149992000 Hz

mode "1920x1200-60"

# D: 149.993 MHz, H: 72.883 kHz, V: 60.134 Hz

geometry 1920 1200 1920 1200 32

timings 6667 20 100 4 6 18 2

rgba 8/16,8/8,8/0,8/24

endmode

Now everything seems better, the timing and image seems very good:

[upload|0Tfk1PkdHzn79JZNZufMz0Taugs=]

Now:

- What’s the difference from video:dev=ldb,1920x1200M,if=LVDS666 and my DTS mxcfb1: fb@0 configuration? I suppose that the if=LVDS666 is not the same as interface_pix_fmt = “LVDS666”;

in my DTS!? - The M in mode 1920x1200M will do some automatic calculation of timing, but it is wrong, but probably do some other thing that my DTS not configure

- How I can setting all in the DTS?

- … Or how I can sett all parameters (timing and pixel clock and vsync=false) in the vidargs at startup?